Other Parts Discussed in Thread: TPS6594EVM

Hello TI Team.

We are following PROC105E5 in our design and want to check some function of TPS6594-Q1.

Q1: The flag should become 1 when UV/OV/ILIM happen but register values are still 0.

overcrurrent the BUCK1 to 5A but 0x5C flag doesn't change.

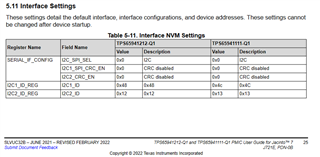

Q2: Why EN_DRV(0x80、0x82) can’t be modified?

Q3: How to check and verify Q&A Watchdog communication?

Thanks and best regards,

Tommy