Dear team,

Recently my customer is testing the power consumption under different states. We have one question below,

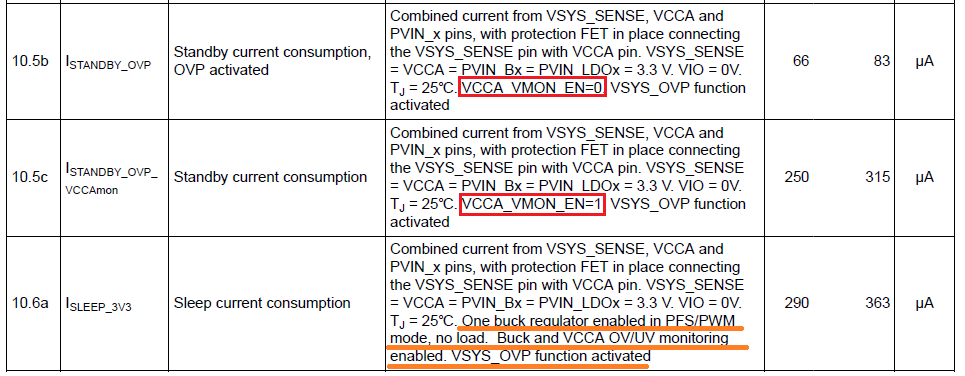

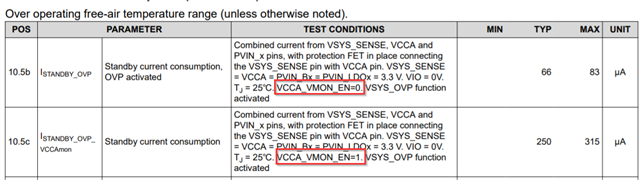

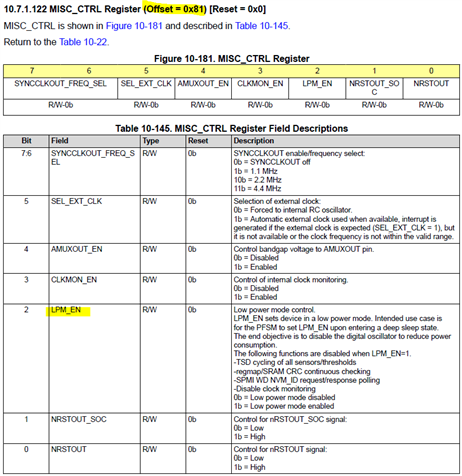

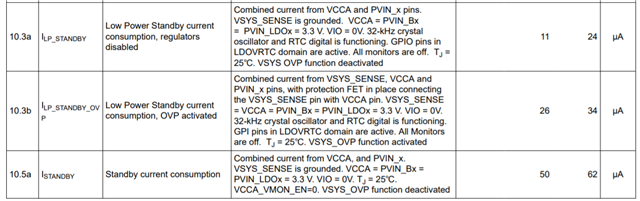

1. What is the difference between Standby and LP Standby? LP Standby mode consume less current compared with standby mode, so which part is disabled in LP standby mode while enabled in standby mode?

Thanks & Best Regards,

Sherry