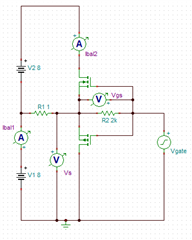

Other Parts Discussed in Thread: TINA-TI

Hi,

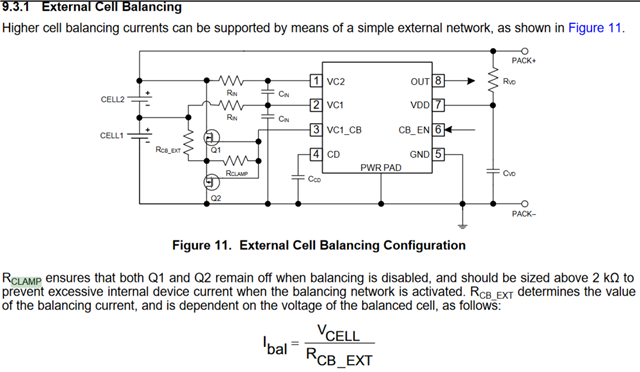

the recommended schematics for external cell balancing might not work like it's intended.

In case of Q1, the Drain Source voltage will be the same as the Gate Source voltage when activated, and because the Source is above the current limiting resistor, the source will start to rise once current starts flowing.

This will start closing the FET and it'll not be in the saturated region anymore.

Same goes for Q2

I believe there should be separate resistors for Q1 and Q2, Q1 drain side and Q2 source side.

Please confirm this, we will manufacture 1k units and I need to add 1A current balancing.

thank you,

Lorand