Dear all,

We are using TPS65132WRVCR in our design. The part is configured at +/5.4V, 40mA, active discharge on both outputs. We noticed some differences with screenshots in the datasheet.

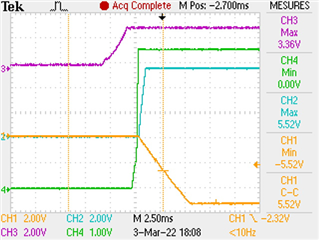

1 - On the following picture there is a spike on VNEG output which is not observed in the datasheet. What can be the cause?

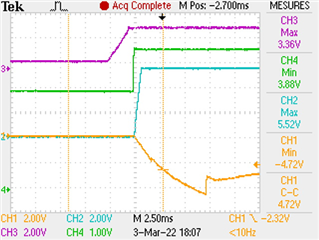

2 - When the device is powered off and powered-on before VREG reach 0V then VNEG does not start correctly and then stays incorrect (about 1.86V which is outside the specified range).

Is it expected that VREG remaining voltage level impacts VNEG startup? Please note that VPOS is correct.

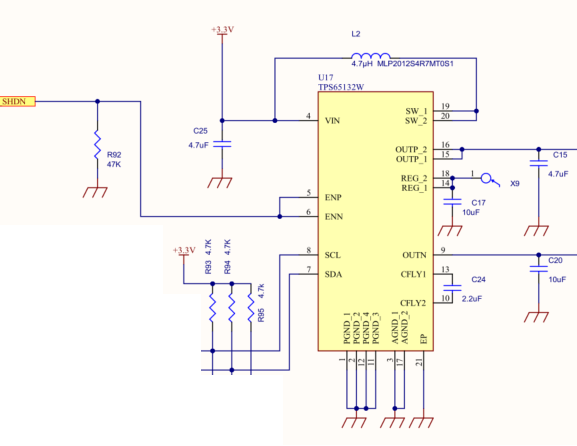

Current schematic for ref. is

Thank you in advance for your time.

Best regards,

Benoît,