Other Parts Discussed in Thread: LM5156H, , LM51561, LM5156

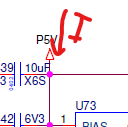

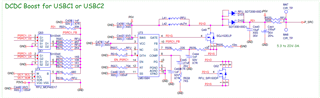

My boost design is the following :

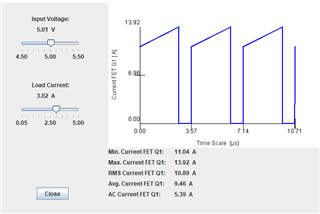

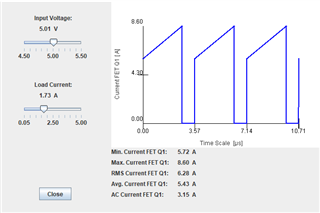

Input = 5V-14A

Output = 9V-3A max or 12V-3A max or 15V-3A max or 20V-3A max, for USBC source application

I select the wanted output voltage by changing the feedback resistor Rfbb.

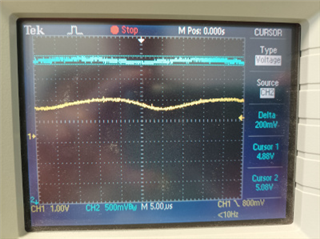

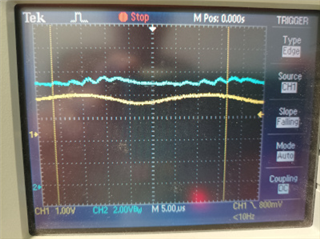

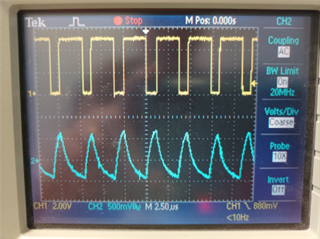

All voltages works well with a light load (~1Kohm).

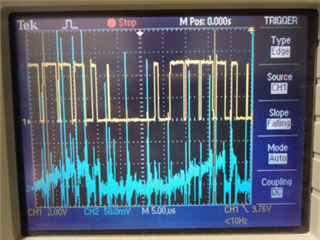

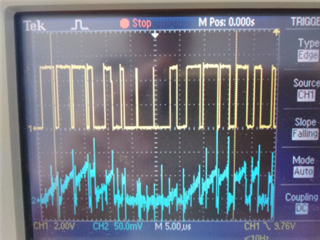

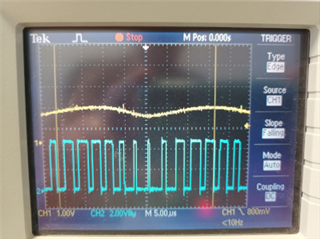

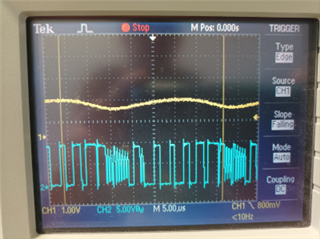

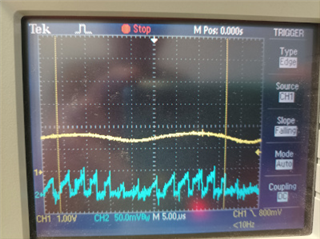

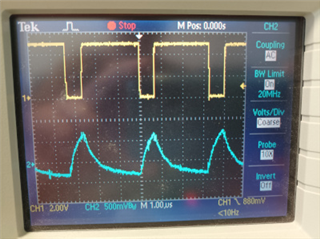

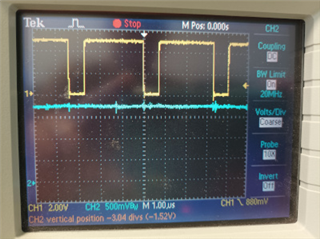

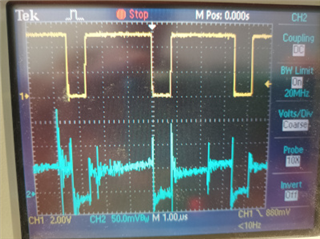

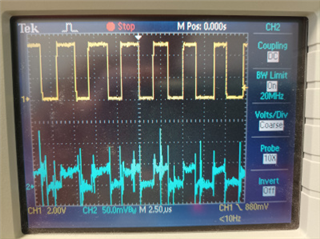

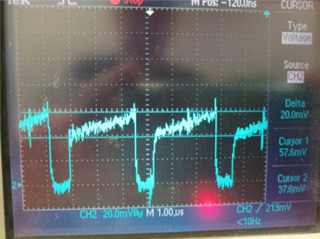

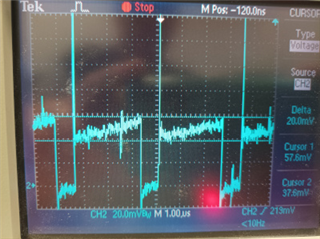

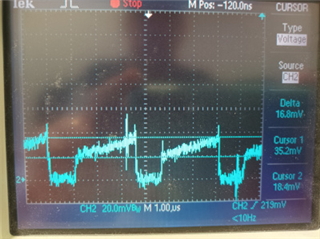

I've tested 9V, it works until 14W, but is not stable after (around 18W). Not stable means that the voltage tries to go to 9V, but decreases to ~5V (chip is Off, I suppose), and retries every 125ms.

I suppose it is the Hiccup Mode Overload which occurs, because on my prototypes, I used LM51561H instead of LM5156H, for availability reasons.

For 15V, it doesn't work @ 12W.

I did several simulations on webench, and selected the worst case values of each component, and make validate my design with FAE in France, but it doens't work.

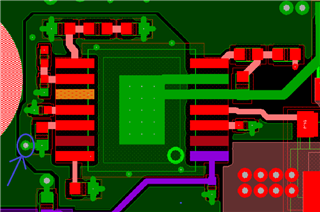

Can you check my design, and tell me what component should be changed ?

Here are the schematics :

Here are the main components BOM :

U73 = LM51561HPWPR, Q49 = SQJ152ELP, D102 = SDT20B100D1-13, L42 = PA4343.472ANLT

All is OK on my board, this is the last stage to make work, can you help me quicly please ?

Thank You.