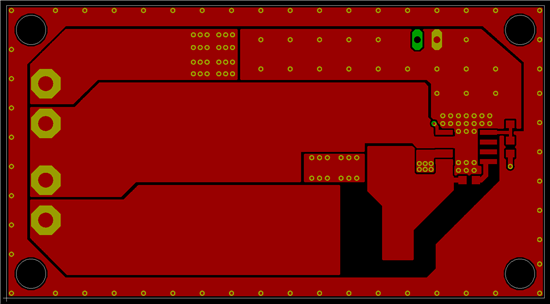

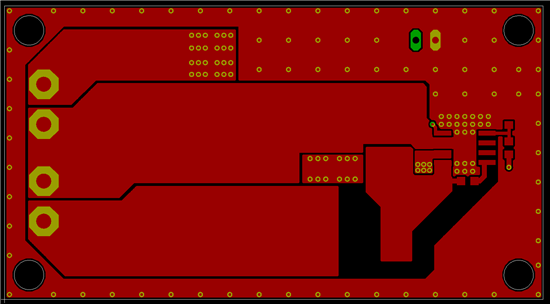

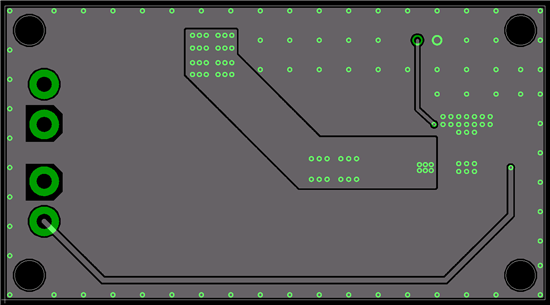

I noticed that the TPS5450 EVM PCB pretty well keeps all the ground current flow on the top layer by keeping the ground planes for layers 2-4 away from the Vin and Vout GND pads and only stitching the ground planes together at the TPS5450's thermal vias, the EN jumper header and TP4. It seems that the GND planes for layers 2-4 are only for heat dissipation and not for lowering GND impedance, helping to reduce emissions, etc.

I'm laying out a board using the EVM's design as a starting point and was wondering what the advantages and disadvantages might be if I "stitched" together the ground planes with vias and also allowed the GND planes to connect to Vin/Vout GND pads? It would certainly lower the GND plane impedance (possibly helping to reduce emissions and increase immunity?) but could that cause problems?

I was also considering enlarging the top layer GND plane and having it essentially encircle the Vout power plane and the components.

Thanks!