Hi TI expert,

Our DDR5 RDIMMs use TPS53832 as PMIC. When we do the following opeations on the I2C/I3C bus,

1. read PMIC register in I3C mode - suceessful

2. bus reset

3. read PMIC registers in I2C mode - suceessful

4. SETAASA

5. read PMIC register in I3C mode - fail

6. bus reset

7. RSTDAA

8. read PMIC registers in I2C mode - suceessful

9. SETAASA

10. read PMIC register in I3C mode - suceessful

It's strange that I3C read opeation in step5 fails. If RSTDAA in step7 is inserted, the I3C read opeartion in step10 is successful. I don't think RSTDAA is necessary, but the reality is that the switching operation between I2C and I3C fails without this procedure (as step 1~5).

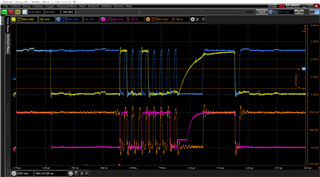

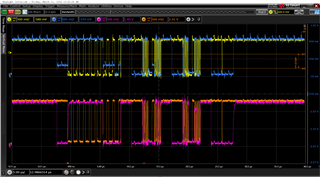

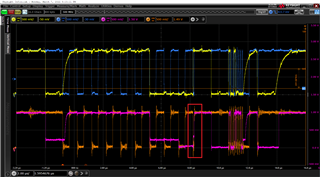

The following pictures shows the waveform in step5. The upper two signals in the screen are on hub host side, and lower two are hub local side(which are connected to PMIC and let's just focus on these two).

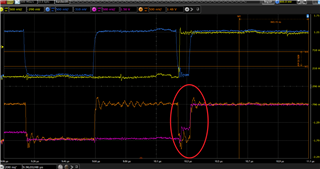

There is no ACK on I3C, and we found a very strange "step" on the data signal in the red circle in the scope screen capture.

The following is a zoom-in view on the circle.

We did the same experiment with IDT PMIC and it works quite well. It means that I3C read operation in step5 is successful for IDT parts.

The below picture shows the TI parts on the DIMM.

Please feel free to let me know if there is anythin unclear.

Looking forward to your reply. This issue has been bothering us for quite a long time and has seriously affected the progress of our project.

Best regards,

Shaoyuan Zheng