Other Parts Discussed in Thread: BOOSTXL-TPS650861, MSP430F5529

Hi TI team,

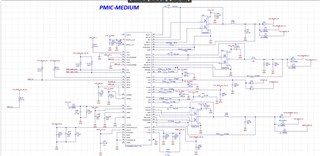

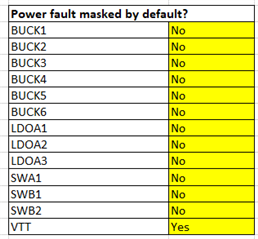

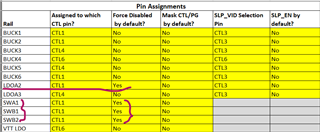

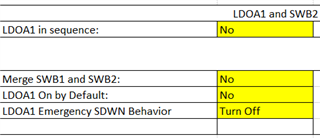

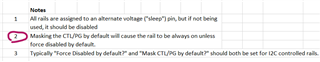

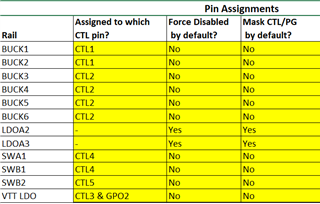

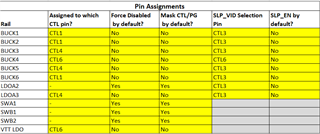

We recently replaced a PMIC after programming (burn) it with a custom OTP using TI BOOSTXL-TPS650861 along with MSP430F5529 LaunchPad Development Kit. We successfully burn the OTP which had configuration to disable LDAO1, LDOA2, SWA1,SWB1 and SWB2 as were are not using them in our design.

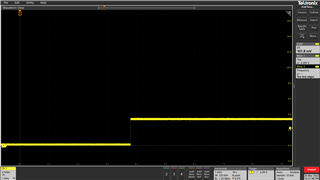

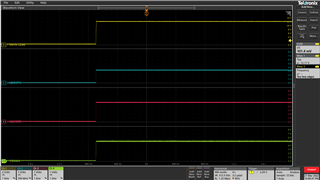

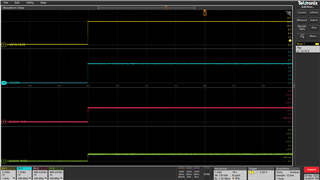

This new PMIC with custom OTP was replaced on to our board and when we powered ON, it worked as expected and then we did a power cycle (Off & then ON) and to our surprise we found that PMIC is in power fault state and then when we read the I2C registers , we came to know below facts,

SHUTDNSRC: PMIC Shut-Down Event Register (offset = 05h) with data set to 05 means UVLO =1 and CRITTEMP=1.

TEMPCRIT: Temperature Fault Status Register (offset = B4h) with data set to 1F means DIE_CRIT, VTT_CRIT, TOP-RIGHT_CRIT, TOP-LEFT_CRIT, BOTTOMRIGHT_CRIT all are set to 1.

Registers B0 to B3, B5 and B6 were all set to 00h means no issues.

But we checked the Temperature externally using a thermocouple probe with multimeter, the temperature reading was within 34 degree C.

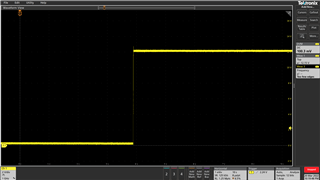

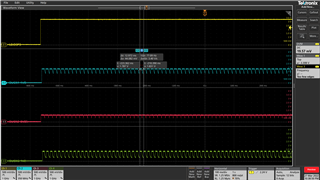

So finally we turned PMIC OFF and waited for 5 to 10mins and then we turned ON and again to our surprise there were no power faults and all the expected rails were up and we even continued working on ZU3 by programming it, at this point we read the I2C registers and still it read same values as above.

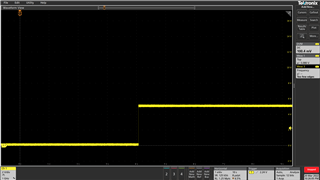

We repeated above steps for 7 times, and the results were same. (that is turn OFF the PMIC and wait for 5 to 10mins and then turn ON it works without any faults, but if you try to turn ON PMIC immediately or less then 5mins after OFF, then it goes into power fault state.)

Bottom line is if you give a time gap of 5 to 10mins between power cycles then PMIC works continuously for hours perfectly fine with no sign of power faults even though I2C registers reading shows above values.

Can you please help me in debugging this issue.

Regards,

Sandeep P