Hi E2Experts,

I have multiple boards designed with TPS6508640 powering a Xilinx ZU3 and ZU2 MPSoC and am seeing some unexpected behavior consistent with all of them related to operating temperature of the TPS6508640.

What we are seeing:

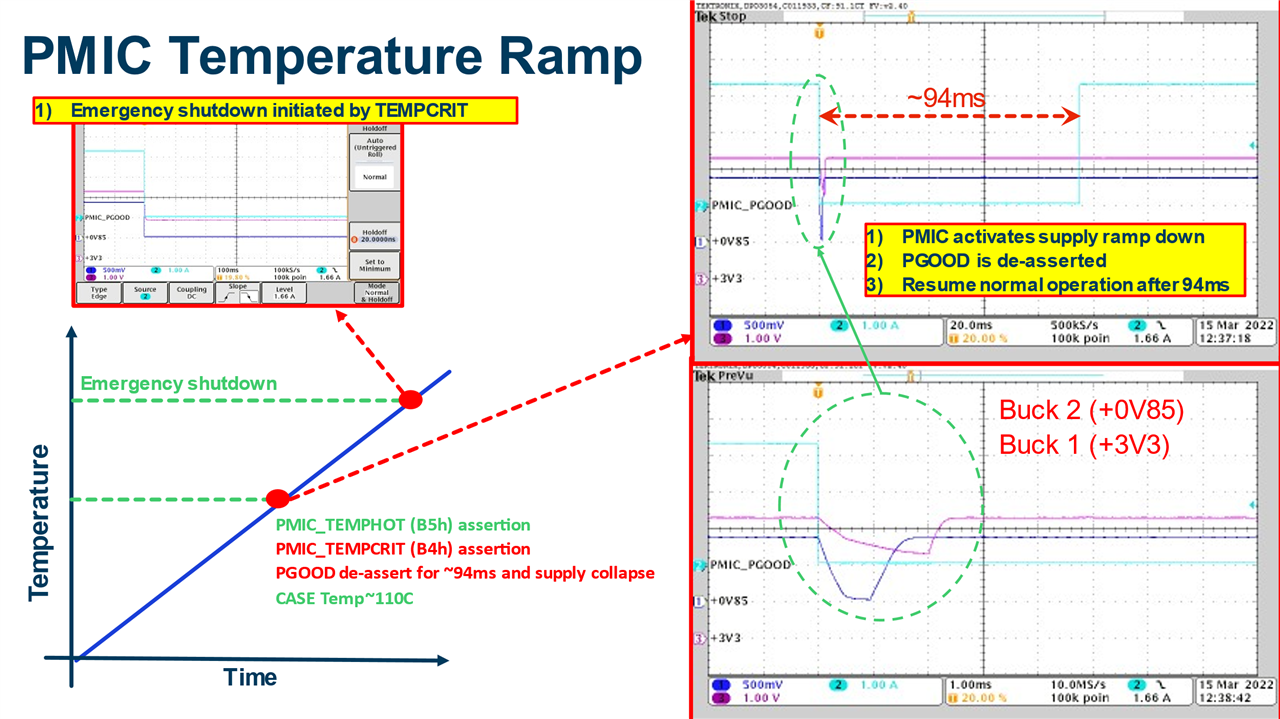

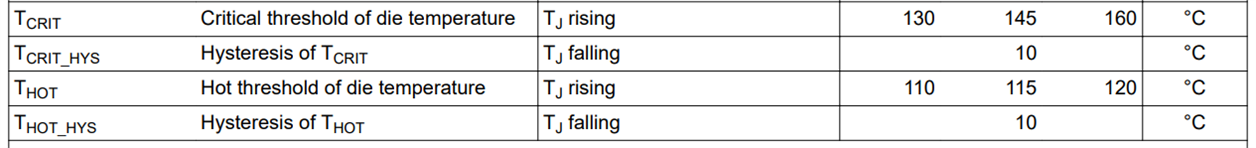

The datasheet specifies the PMIC will enter emergency shutdown (section 8.10.7 in SWCS138D) when TCRIT is reached, and that temp is in the DS as min 130C. No mention of THOT is made in this section. Behavior of the TPS6508640 when reaching THOT is not described in the DS but can be inferred from the lack of info that no rail sequencing is expected at this threshold.

Yet we are seeing TCRIT being improperly asserted in the register 0xB4 at a case temp of ~110C. From the Psi-JT parameter and our total dissipation on the entire board being <6W, Tj is expected to be ~112C, far below the TCRIT value.

The erroneous assertion of TCRIT correlates to the momentary shutdown of our power rails that are immediately resequenced because our ENABLE PIN (CTL3) is tied to a power good indication from a supervisor looking at the TPS6508640's input voltage.

When we exceed a case temp of 130C, no flags change in the registers as TCRIT was already asserted at the THOT threshold, then we see the expected and described emergency shutdown where rails drop discharge and remain discharged until the case cools to ~TCRIT-TCRIT_HYS.

So can you please help explain why the TPS6508640 momentarily brings the rails down when passing the THOT threshold. Where in the DS it describes this behavior? Where we can find a description of the thermal monitoring block as shown in the PMIC Functional Block Diagram. And is there something that can be done to bypass this behavior?

Best Regards,

Rob Rodrigues