Hi,

We are designing 5kW PSFB converter using UCC28950 as VMC.

For the secondary side, a full wave diode method was applied.

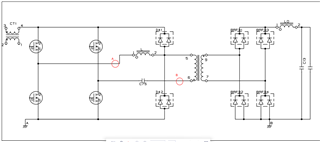

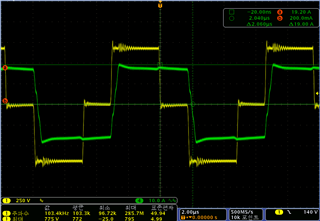

Fig 1

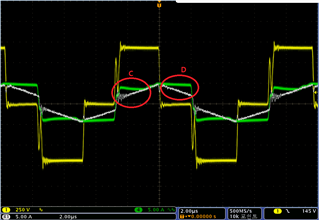

The waveform in Figure 1 are the primary side current and voltage waveforms measured under the 30% load condition.

When the DC blocking capacitor is applied at 2uF, the current in the red circle looks like a DC current.

In this state, the converter is damaged when it is operated for a long time.

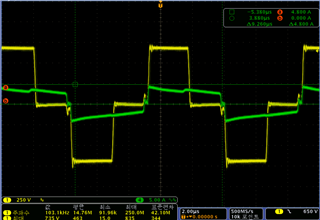

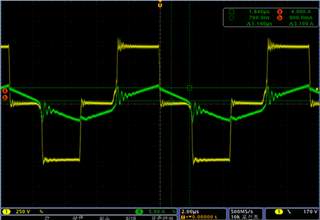

Fig 2.

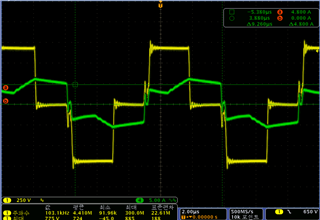

The waveform in figure 2 is a waveform measured by adding a dc blocking capacitor and applying 5uF.

The dc current in the red circle in Fig.1 is not visible.

In this state, it is not be damaged even if it is operated for a long time.

What is the difference between the two current waveforms?

Can the current waveform tell us why the converter is broken?

Or should I think there is a another reason?

And please advise on what criteria should be selected for the voltage withstand voltage of the DC blocking capacitor.

In terms of measurement, it is currently measured around 25Vp-p ,

but I have seen some data say that it has to withstand the input voltage.

Best Regards,

KW.