Hi,

For my power down sequence of TPS65086401 (as the PMIC for XIlinx Zynq US+ MPSoC), we observed the below:

- CTL1 starts to power down later than the other outputs

- Some abnormal steps in GPO1 / CTL6 , GPO3 / CTL4 and GPO2

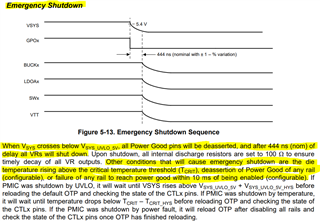

The reference power down sequence seems to be should be like this:

Is the power down sequence acceptable? What can be possible causes.?