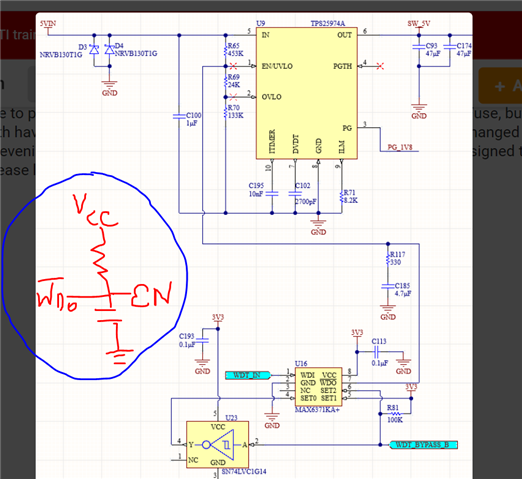

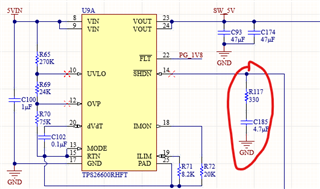

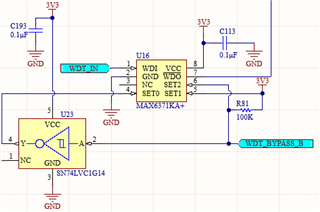

So I have a circuit here that utilizes a watchdog output assertion/deassertion for the SHDN pin of the TPS2660. I believe the delay of the watchdog output is about τ = 4.7uF*1MOhm [internal pullup of SHDN] = 4.7s(?), with a negligible difference with R117 (used for current-limiting). The timer is MAX6371KA+, and the WDO is an Open-Drain Output.

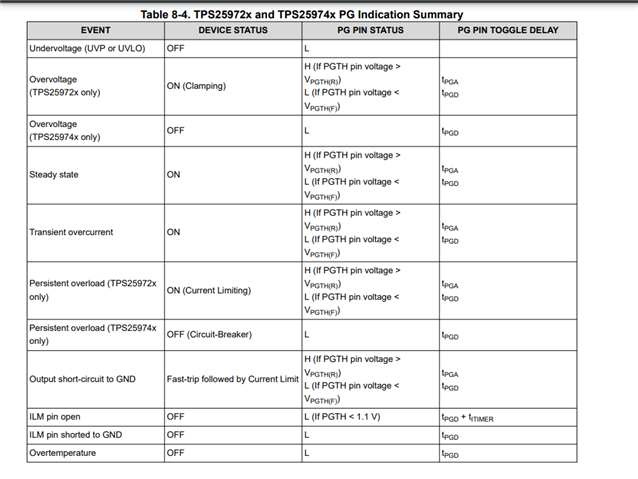

I would like to transfer this design to the TPS25974, due to parts availability. I've nailed down most other functionalities of e-Fuse, but the TPS25974 does not have a SHDN pin, so I am stuck with having to use the EN pin for the TPS25974. Does C185 need to be changed in the updated schematic (below) to take into account the Thevenin resistance network of IN/UVLO/OVLO? My ex-coworker had designed the delay, and I'm not sure if the delay calculation is truly 4.7s. Please let me know if I unclear about any details.