Hello Everyone in the forum,

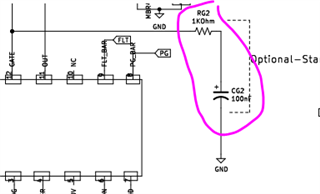

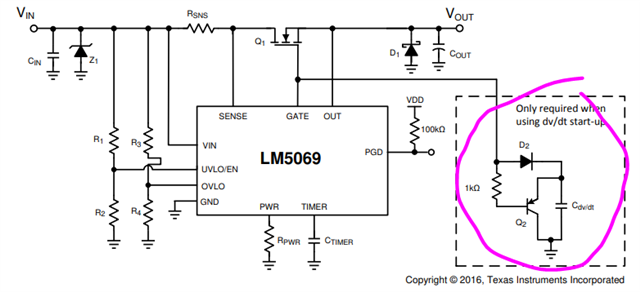

We are designing a soft starter controller for our vacuum motor using the TPS2492 chip.

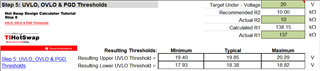

We have attached the design calculator for this motor which is running at a maximum 24V, 25A.

The motor load has an inductance of 0.763mH and 0.8ohm.

Recently we have tested the circuit and the MOSFET that we are using caught fire.

I have filled in the calculator accordingly and seems there is no problem with the calculation

CSD18534KCS 24V 5A.xlsxTPS2492Test.pdf

There are a few observations on our test:

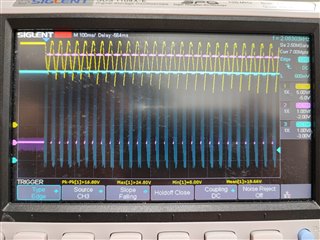

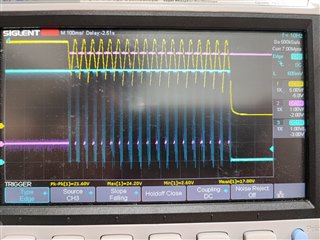

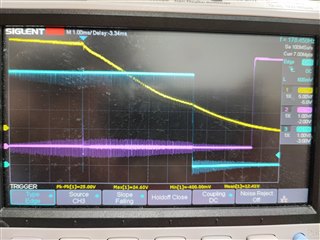

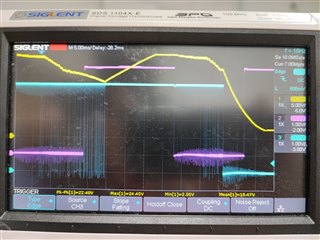

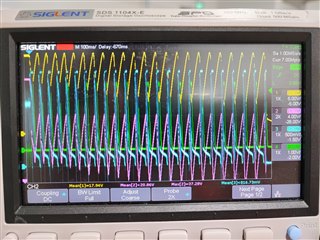

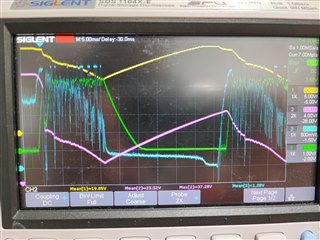

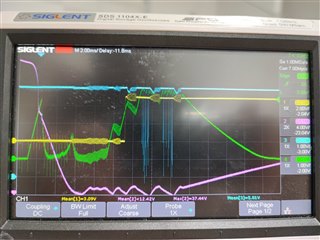

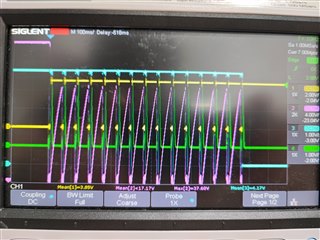

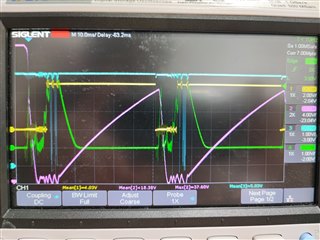

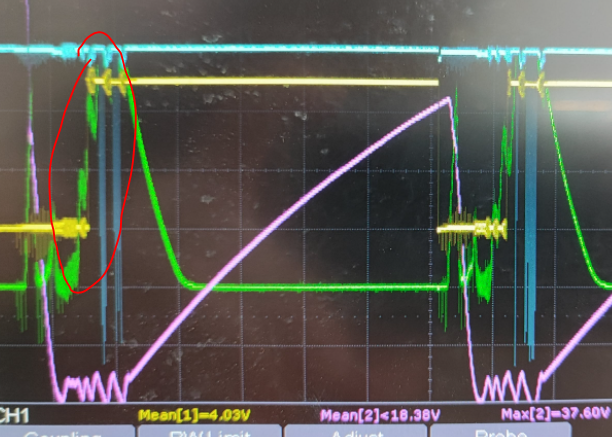

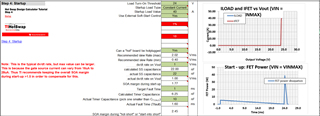

- When the load current just exceeds the limit, around 5A, the PG and Vout start to react up and down which seems uncontrollable, according to the datasheet, it should cut off after the timer set by CT and never turn on again, apparently not in our case, and the fault is never going to 0V or LOW as a sign of FAULT

- When the above happened, the MOSFET seems like on the resistance area which actually has a lot of power loss and it is ongoing without the TPS2492 cutting it off.

Is there anything that we miss in this design? I need some help or maybe suggestion that probably TPS2492 is not the right choice

the requirement needed are

- Overcurrent and short circuit protection

- Undervoltage Protection

- Soft Start for Inrush Current

- Handle Inrush Current caused by a sudden increase of load because of the sudden loading on the motor torque without cutting off the entire circuit