Other Parts Discussed in Thread: TPS61194

Hi team,

I received some questions about TPS61194-Q1 start up and shutdown sequence. Please support.

- Figure 19 mentions the period T = 50us from VDDIO/EN to LDO shutdown. I think the CLDO is 1uF. My customer is using 2.2uF for CLDO but, is there any effect for the shutdown period?

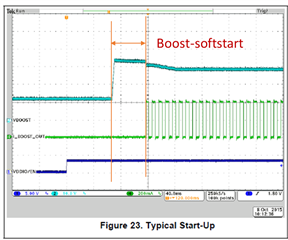

- Figure 18 mentions BOOST START=50ms but actual BOOST START time is much much shorter as shown in Figure 23. Please provide correct value of BOOST START time.

- How much tolerance should we expect for SOFT START time of 65ms and BOOST START time?(expected answer is +/-10% or so)

- My customer controls an OUT-pin by transistor and turn off the channel if the LCD has only 3 strings. When does TPS61194 sample the OUT pin voltage to check use or unuse?

Regards,