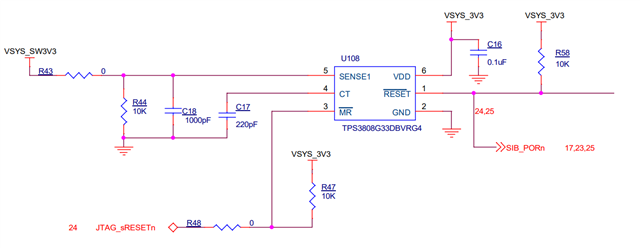

Below is a the schematic of the TPS3808 circuit:

The power on sequence is VSYS_3V3 first, followed by a ~1s delay, and then power on VSYS_SW3V3. The ramp time for both supplies is approximately 10ms. I have found that on some boards built with this circuit, there will be a glitch on the RESET signal. The cause for the glitch is still under investigation. But the steady state result is for both VDD and SENSE1 to be at 3.3V, but RESET is low. See below for the oscilloscope picture:

The blue line is VDD, and the pink line is SENSE1. 500 microseconds after the reset is released, something causes the RESET to be pulled low again. This is the small, positive pulse you see at t=0. The cause for this is yet to be determined. However, after ~14ms of delay, the reset is released again and stays released for about 10ms. After 10ms, the reset is pulled low (again, cause unknown) and this time it stays that way permanently. I do not have any latching circuitry connected to the RESET signal. VDD and SENSE1 are both greater than 3.3V, so I would expected RESET to be released. Do you know of anything that could cause the IC to hold RESET low? There is no external circuitry that could be holding it.

-Zack