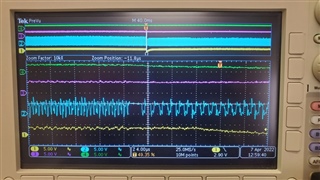

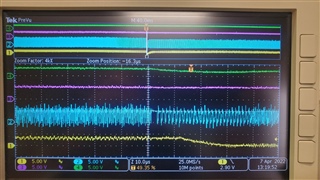

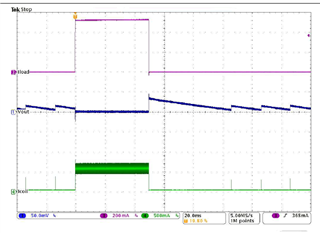

We have a system that undergoing testing. When the system is operating is a steady state (no changes in power requirements) we introduce a physical shock of several hundred Gs. When we observe the SW output signal we can see that it transitions to Low Power mode of operation, which immediately causes the regulated output (3.3V) to drop to about 1 volt before it switches back to PWM mode. Through all of this there is no change in the input voltage.

Is there a way to force the regulator to stay in the PWM mode? How can we determine what is causing the switch to Low Power operation.

Or is there a part that would be a better choice.