Hi,

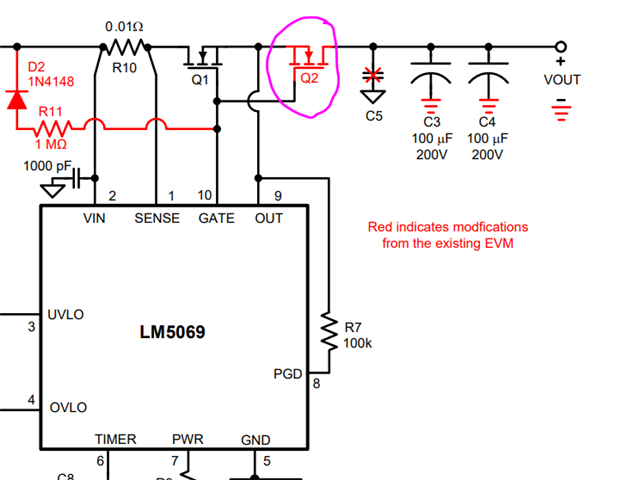

I have a LM5069 design which is providing switching/protection of a nominally 48V output from a control card. In long-term running the design is fine but we've now had two device failures in power cycling testing with our load (after 300 cycles and 2000 cycles on different boards).

Once the device has failed an attempt at start-up (controlled by OVLO) results in a fault as the duration in FET power limit is exceeded. We originally suspected that the FET may have been overstressed but replaced the FET and still had the issue. We had to replace the LM5069 controller to correct it.

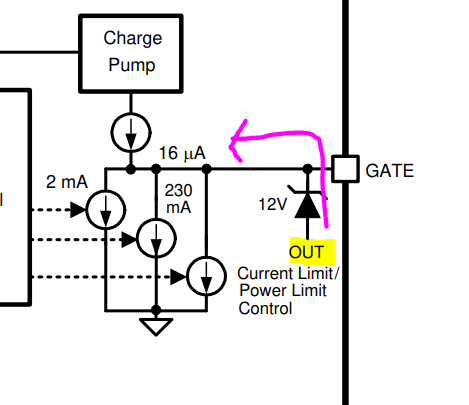

Investigation shows that the gate voltage driven by the "bad" controller during the power limited start-up phase is lower than on a "good" controller. As a result, the FET passes less current, doesn't manage to establish the output voltage in time and the controller goes into fault.

Please can you suggest potential causes of the damage to the controller that might yield such a symptom that we can investigate in the system?

Is there any other data that we can provide which would be useful in helping you to help us to identify the root cause of this failure, which we urgently need to resolve?

Many Thanks!