Hi team,

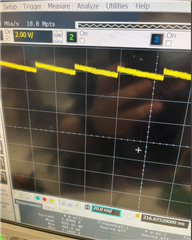

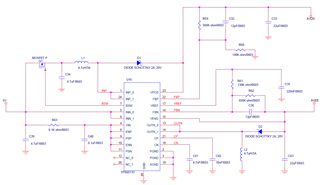

Would you help to review the schematic design? Customer reported the output ripple is too big. Thanks.

Regards,

Alex

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Alex,

The schematics did not come through in your post and I could not see them. Can you please re-attach?

Kind Regards,

Liaqat

Hi Liaqat,

I attached the schematic again here. Please help to check and provide comments. Thanks!

Regards,

Alex

Hi Alex,

I reviewed the schematics and one change that I could suggest is to tie PSP/PSN (pin 9/11) to GND instead of Vin that it is currently tied to. When PSP is tied to Vin, boost can go into PFM mode during lighter load and can have a significant amount of ripple. For ripple sensitive applications, we recommend to tie PSP/PSN to GND so that the device stays in constant frequency PWM mode which has a lower and much stable ripple.

Kind Regards,

Liaqat

Hi Liaqat,

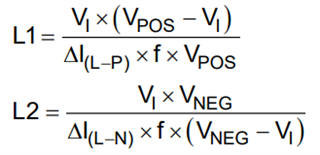

Thanks for your comment. Do you think increase L1/L2 to 5.6uH also help to reduce the ripple(reduce inductor p-p current)?

And do you have the design tool can share with me? Thanks.

Regards,

Alex

Hi Alex,

Increasing inductor value may help slightly but I would not recommend it as it may have some impact on loop stability and all validation on TI evm was also done with 4.7uH. I still suggest to tie PSP/PSN to GND to achieve lower ripple.

Kind Regards,

Liaqat