About TPS54218 setting compensation network based on datasheet equation (11)~(18), condition is below.

→Vin:5V, Vout:3.3V, Iout:1.3A, fsw:1.8MHz, L:2.2μH, Cout:22μF

→R3 (Rcomp):10kΩ, C1 (Ccomp1):5.6nF, C2 (Ccomp2):2.2pF

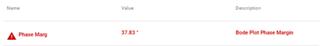

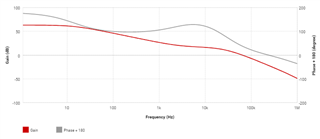

When above value insert to Webench, but phase margin become low margin.

Webench report is shared below,

https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=424A3F69C1370892

Please let me know about the reason for gap by Webench and equation.

(Or, is these result Webench's bug?)

I thank that recommend to setting is based on equation (and actual measurement), is it correct?

By the way, When TPS54218 board measured below condition, it was good transient response.

But Webench simulation was low phase margin. (Less than 40°)

R3 (Rcomp):15kΩ, C1 (Ccomp1):1nF, C2 (Ccomp2):Not mount

Best regards,

Satoshi