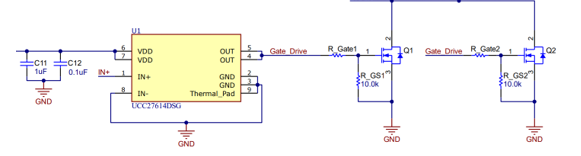

Other Parts Discussed in Thread: UCC27614, UCC27322

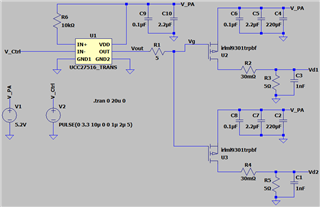

I need a gate driver for a front end power amp switching application - A Power MOSFET switches the drain bias of a PA on and off with a p-channel MOSFET configured as a high-side switch. I was considering using the UCC27516/7 but the application descriptions only mention low-side use. As far as I can tell, there doesn't seem to be a reason why this couldn't work for a high-side P-Channel MOSFET. In fact, Spice simulations seem to show that it works when I set the device up in an inverting mode.

Am I missing something? Will the UCC27516/7 performance be undesirable in some way?