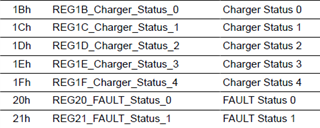

I am seeing a large momentary dip in the SYS voltage when starting the battery charger at 4A of charge current after the system current limit has been updated to 3.0A and the input voltage has been updated to either 9V, 15V, or 20V. The dip becomes larger at the greater voltages and it is most noticeable to me when the battery voltage is low to start charging since SYS dips low enough to trip my external UVLO (completely separate from the BQ UVLO). While I could lower my UVLO (set at 3.3V for SYS rail) to accommodate this blip, I am curious to know if it is expected and if there is anything I could do to reduce it.

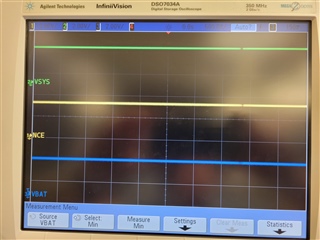

Here are the traces I captured. VSYS, VBAT, and NCE (charge enable; active low)

Here are the levels of VBATT and VSYS with only the battery connected. No input voltage to the BQ charger at this time. VBAT average value is ~3.3V and VSYS is slightly higher. I recorded min and max in this screenshot.

When I use a 9V charger or 15V charger, I can apply USB voltage, negotiate PD, the PD part sets up the BQ registers for charging, and then my system enables charging (nCE signal). This works fine with these 2 AC adapters. You can see that below. While nCE seems a bit noisy, the system boots, no UVLO is tripped (3.3V level), and the system starts charging the battery.

When I use the 20V adapter, I see problems. The SYS dip is more pronounced and it hits my UVLO, which sends my system into reset and this toggles the charging line high (nCE) to disable charging. This process basically repeats itself over and over unless I increase the battery voltage a bit before applying USB power. Perhaps I would charge just enough over time that it would eventually escape from this condition, but I have not attempted that test.

Is there any sort of soft start I can enable or something I can add in hardware externally to reduce this momentary dip? Does it indicate a weakness in my hardware design or layout? Should I simply move my external UVLO to a lower voltage?