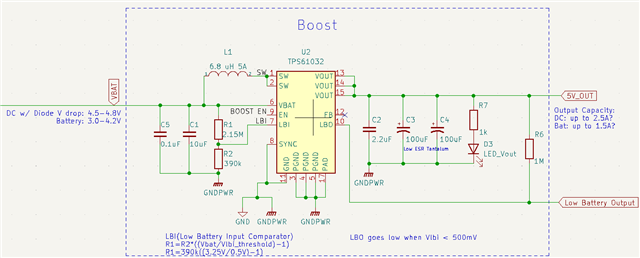

I'm using the TPS61032PWPR in a new design. Input:

5V DC after diode V drop: 4.5-4.8V

Battery: 3.0-4.2V

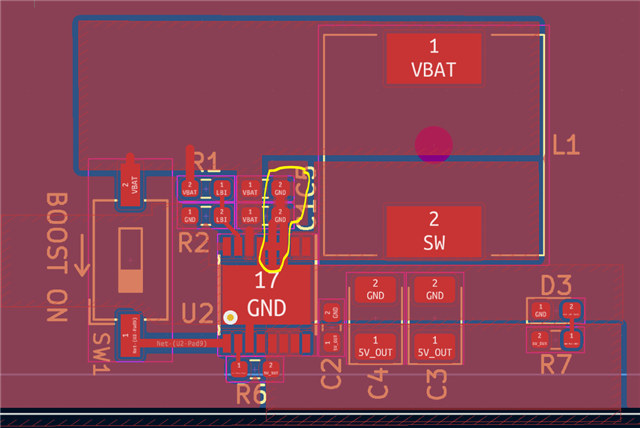

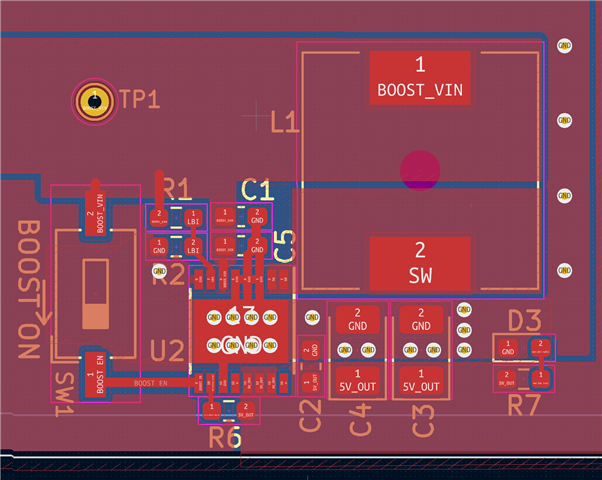

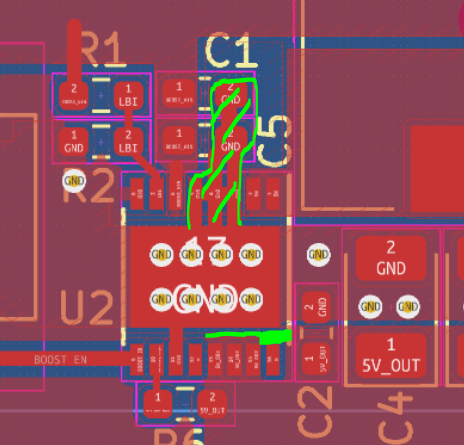

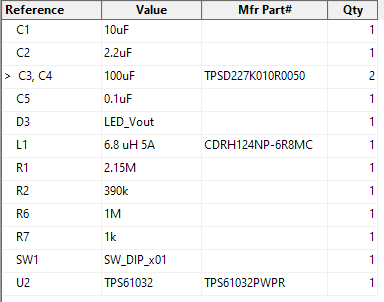

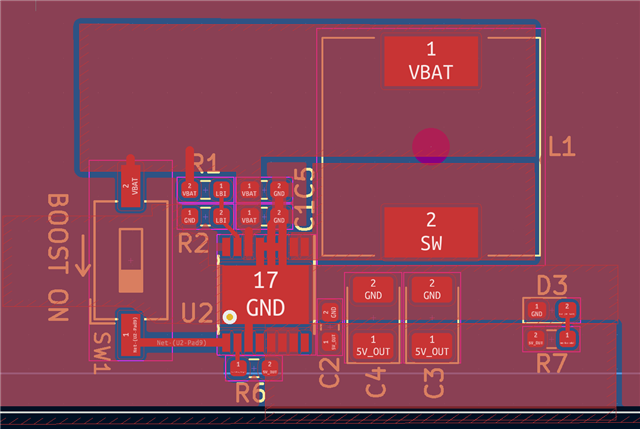

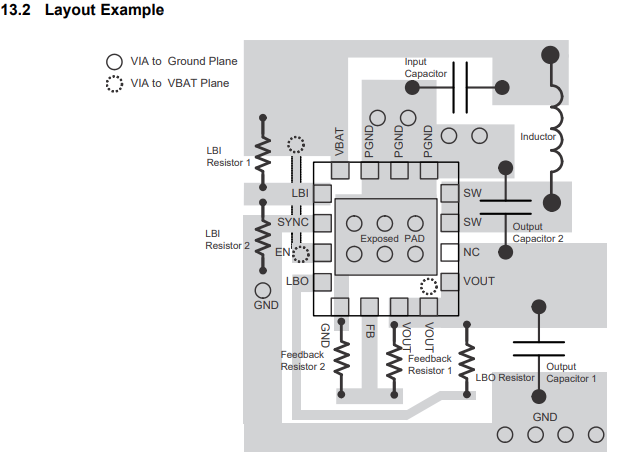

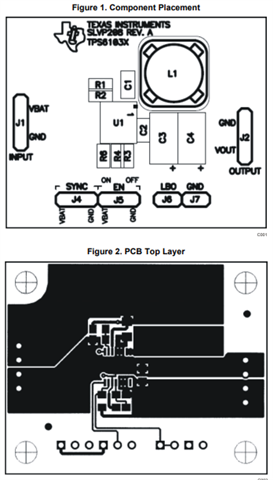

Since I'm using the TSSOP package the layout is based closely on the TPS6103x EVM-208 datasheet in addition to the TPS61032 datasheet. I'm looking for general feedback on the schematic and layout, and I have a few questions as well:

1: The layout example in the TPS61032 part datasheet shows many vias to ground (by the input and output caps, in the thermal pad, and by LBI resistor 2). but the evaluation module layout just has 1 via to ground near pin 9. Which method is preferred?

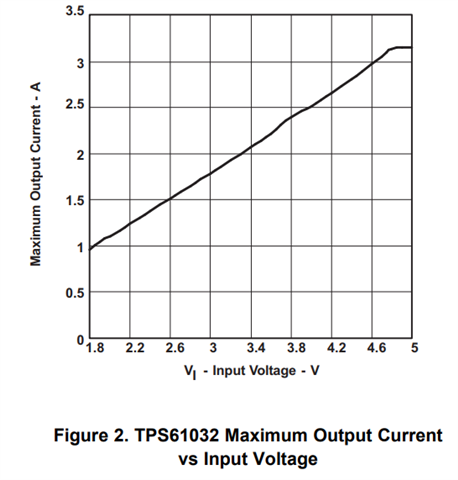

2: Based on my inputs (DC 4.5-4.8V and Bat 3.0-4.2V) and Figure 2 of the datasheet. It seems that I should be able to get at least 2.5A+ when using the DC supply, and 1.5A+ while using the battery supply. Can this graph be taken at face value or are there other considerations that limit the output current?