Other Parts Discussed in Thread: UCC28951

Hi Team,

It is an application using UCC28950, and it is designed to be set as a slave and operate at a synchronization frequency of 190kHz from the outside.

Often, there is a mode in which the High / Low time of the C and D drive outputs becomes long.

When I checked the threads in the past, I confirmed that the same mode occurs when the Duty is 90% or more and the overcurrent state occurs.

I tried changing to UCC28951 as a solution, but this mode is still occurring.

Please give us some advice on the cause and solution of this mode.

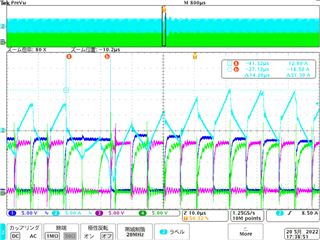

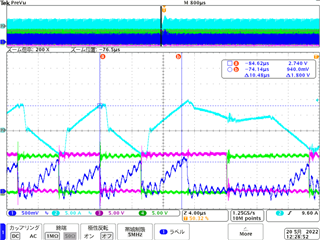

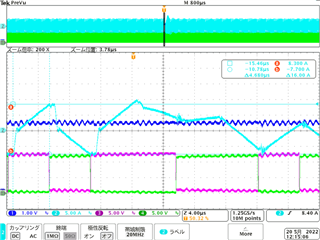

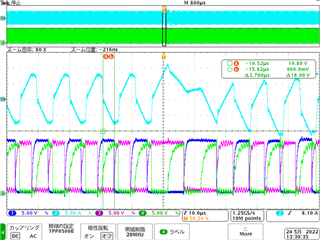

Please see waveform below;

-CH1 C_FET_Vgs

-CH2 transformer current

-CH3 D_FET_Vgs

-CH4 B_FET_Vgs

mode1

mode2