Hi,

In the design we use TPS650861 to power up NXP LS1046 processor.

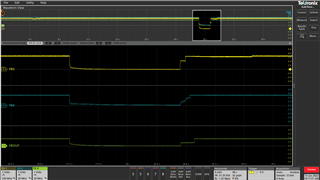

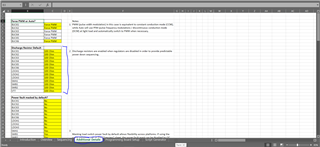

Power sequencing is as follows : CTL1 will power up Buck3> Buck 4> Buck 1 >LDOA3 CTL2> Buck 2 and CTL3 >Buck6.

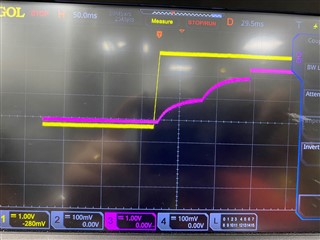

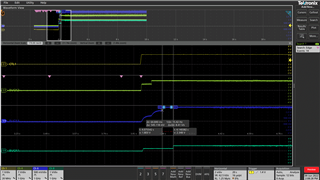

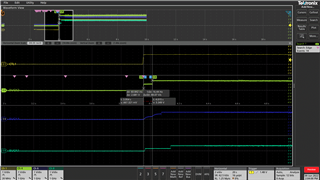

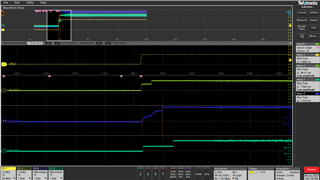

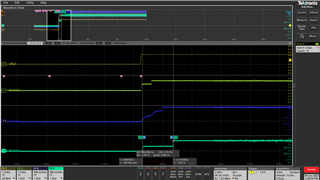

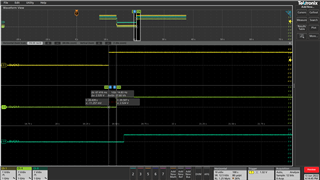

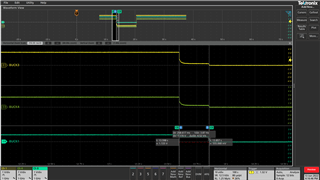

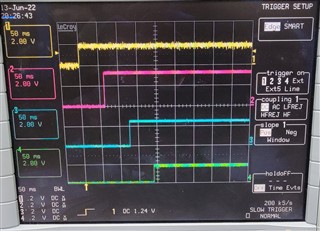

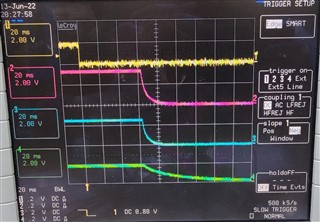

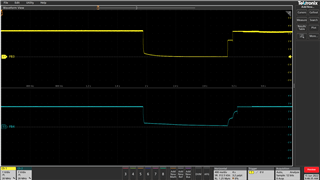

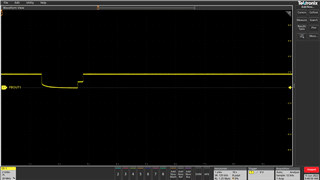

We are facing issue with transient response of Buck regulators(4,3,1) in CTL1 sequence.

Buck 3 is the first rail powered on. Buck 4 rail is sequenced based on CTL1 and PWR good of Buck3 . Buck 1 is sequenced based on CTL1 and PWR good of Buck 4.

Ramp up is not smooth for all the 3 rails. OTP programmed for DVS enable, Step size of 25mV and Rise time delay of 64ms.

Attached the OTP generator sheet and Waveform capture for Buck 3 and Buck 4 .

CTL2 and CTL3 voltage rails are fine. Is there a way to improve the transient response . Please advise.