Other Parts Discussed in Thread: LM51561, LM3488

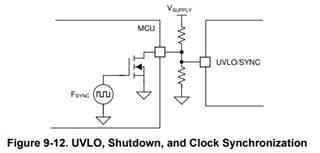

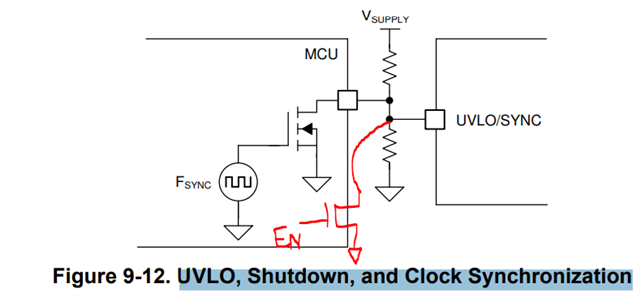

I want to use the external clock synchronization function on the LM51561.

External clock is planned to be made in FPGA, 3.3V level, 120KHz.

Please refer to Figure 1 below for details.

The specification of the required external clock could not be found in the datasheet.

There are electrical properties related to UVLO/SYNC on page 6 of the datasheet, but I don't quite understand.

The working scenario is as follows.

When the system boots for the first time, it operates with the RT-set resistance value, and when the FPGA is downloaded and initialized, the FPGA will provide an external clock.

I ask you three questions below.

1. Inquire about synchronization signal threshold specifications (High level, Low level).

2. In Figure 1 below, I ask if there is any problem even if you use it like R13 and C19.

3. If you can use it like R13 and C19 in Figure 1 below, please inquire about the formula to set the R/C value.

4. If there is a better way, please suggest.

For reference, the example below is an example of the external clock spec in the LM3488 data sheet.