Other Parts Discussed in Thread: TL431

Hi

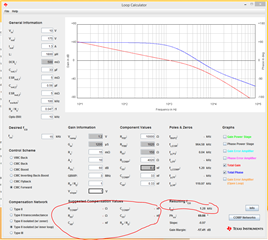

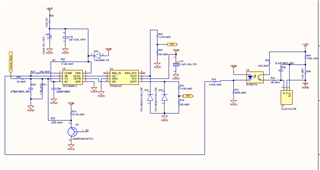

We have designed push pull converter using IC UCC3808-2. Input is 10 ~ 60V DC input from battery and output is 170V DC. Generated 170V DC is fed to inverter to get 110V AC output.

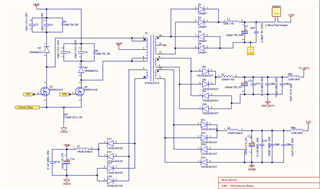

Please check attached snapshot of design.

transformer primary inductance is 0.308uH (3 turns on each winding) and secondary inductance is 1.53mH (63 turns). Board is up successfully and tested with load of 60W.

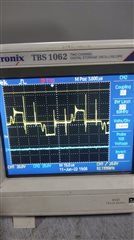

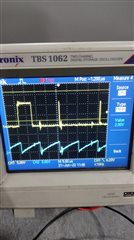

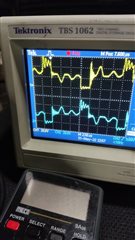

Issue with the board is, Vds waveforms of Q5 and Q6 is not as per ideal waveform. Ringing observed on Q5 when Q6 is turned on and vice versa. Also there is ringing in current sens waveform. Please check images of waveforms for your reference.

Ch 1: current sense input to IC U5; Ch 2: Q6 Vds

Ch 1: current sense input to IC U5; Ch 2: Q6 Vds

Ch 1: Q5 Vds; Ch 2: Q6 Vds

Ch 1: Q5 Vds; Ch 2: Q6 Vds

Can you help me to resolve this errors in waveforms? Let me know if you need any other information.

Thanks and regards,

Ankit