Hi there,

I'm trying to set up a version of this where I modified your board to accommodate a high-frequency socket. So far, I've managed to get communication working and get an output on BUCK1, BUCK3, BUCK4, BUCK5, and BUCK6, although I'm experiencing a surprisingly high current draw resulting from BUCK6 which increases non-linearly as I modify the BUCK6VID register (0mA at output=0, increasing exponentially until around 300mA at 1.45V). BUCK

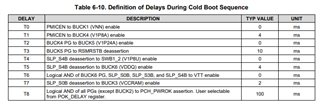

I'd like to ensure the startup sequence works how I think it does. First, VSYS turns on (I have 13V). Then the internal regulators should turn on, then the external regulators must come up, then PMICEN should turn to high. Is there any specific maximum timing delay constraint that must be met in order to ensure proper operation? If the external power were supplied through an external source such as two power supplies instead of using the suggested TPS51285BRUK, would the delay of manually starting those cause issues?

And about the blue arrows on the cold boot sequence on page 41 of the datasheet. Do those represent dependency? Could you elaborate a little more on those?

Kind regards,

Aaron