Hi

sorry bother you guys again.

the output volt ripple is 850mV at 1.5A Io

and i found SW note is unstable

please see my attachment.

the conditions as below

Cin:22uF*3+10uF

Co:22uF*2

Vin: 4.2V

Vo: 3.3V

Io: 1.5A

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

sorry bother you guys again.

the output volt ripple is 850mV at 1.5A Io

and i found SW note is unstable

please see my attachment.

the conditions as below

Cin:22uF*3+10uF

Co:22uF*2

Vin: 4.2V

Vo: 3.3V

Io: 1.5A

I'm sorry you're having problems. The IC does work fine under these conditions and you can order to EVM to prove it. Is this testing being done on the EVM or your own board?

The schematic you sent uses very different components than what you mentioned in your post. Did you use what was in your post or what is on the schematic? Can you post the inductor part number that you used?

What is your input supply current limit?

Chris:

My solutions as follow:

Cin: 22uF*6 (MLCC)

Co: 22uF*4 (MLCC)

BUT if Cin less than 22uF*5 ,the unstable problem will occur that i mention before.

Why input capacitance need so much??

Operation conditions:

Vin: 3.2~4.2V

Vo: 3.3V

Io: 1.5A max.

L: 1.5uH

I am glad you solved this issue.

The TPS63020, and almost all ICs, require a low impedance Vin connection to their input source. This is provided by the input capacitor and the input network in front of the input cap. If more input capacitance solved your issue, then this means that the impedance from your input source (input source itself or the wires and traces between it and IC) is too high. Thus, when the IC wanted current, it would get that current across your input impedance and this would cause the voltage to drop. It would eventually drop below the UVLO level at which point the IC would no longer pull current and the voltage would begin to rise. This would repeat.

It is important to test your circuit with the final components and configuration that will be used in your end system. This means, final input source, input wire harness, input and output connectors, final enclosure/packaging, etc.

Chris:

my DC power supply (Agilent's equipment) have voltage compensation ready to tps63020EVM input terminal

so voltage drop can be ignored , but tps63020EVM input capacitance is very large at (150uF+22uF*2) in original ,not like others tpsxxxxx EVM's may be 22uF or 44uF.

In practice , i fined tune the EVM for client's spec ,it is really need more capacitance (22uF*6) for input side and SW note can be stable.

my client need to know why input need so big capacitance?

if you have EVM , you can try my test condition for reducing input cap to see SW note stable or not.

Your remote sense connections on your power supply are good but they only overcome real (R) losses in the cables. They do nothing to reduce the impedance (L+R) of the cables and this is why more input capacitance helps. Decreasing the AC impedance at the IC overcomes the relatively high AC impedance of your power supply and its cables. Also, is the power supply connected directly to the input of the IC or are there more circuits between it and the TPS63020?

What voltage rating and dielectric are your input caps? Y5V and Z5U hold their capacitance poorly as a DC voltage is applied to them. They could possibly lose 90% of their nominal capacitance at your conditions.

How will this device be powered by the customer? The key is to make sure that it works when powered in the application not in a lab environment. This may require more or allow less input C.

We are currently testing the EVM in our lab by removing the input caps. We hope to have results by the end of the day.

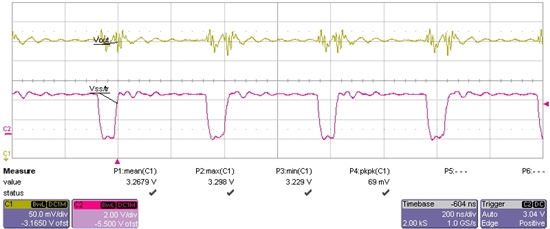

Attached is a scope capture of the output(c1, yellow) and switch node(c2, pink) with only C2 and C1 input capacitors on the EVM board.

C2 = 22uF, C1 = 2.2 uF

Vin = 4.2 V, Vout = 3.3 V

No instability is observed with only this 24.2 uF of Cin.

Hi,

Please see attached test results.

Regards,

Sheronda