Hi Experts,

While using the TPS7A63-Q1, after the device power on,

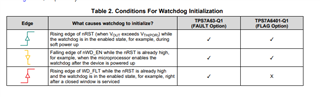

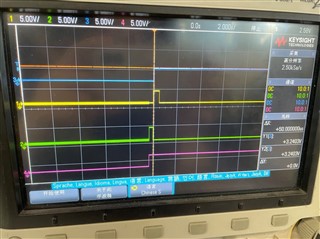

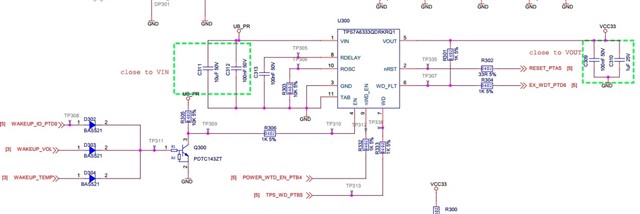

- nWD_EN Pin keeps LOW, WD Pin keeps LOW as well, how should WD_FLT Pin responds under this condition?

-

nWD_EN Pin is HIGH at first(turn to LOW 2s after power on), WD Pin keeps LOW all the time, how should WD_FLT Pin responds under this condition?

During the real test, the WD_FLT are always HIGH under these two conditions. I would like to learn how should it act?

BR

Frank