Hi,

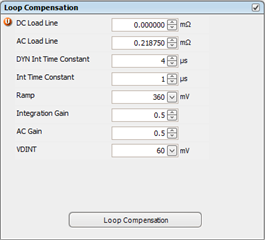

I'm using TPS536C7 multiphase PWM controller. Using the loop compensation parameters as shown in the below image, I'm getting around 22° phase margin. Please suggest on how should I change these parameters to achieve phase margin greater than 65° phase margin.