Other Parts Discussed in Thread: TLV320ADC3101, TPS7A20

I'm designing a battery-operated device, and I use the TPS79330DBVR to supply the AVDD for an ADC chip (TLV320ADC3101).

The ADC can be configured to consume close to nothing and this is used when the device is sleeping, to conserve battery.

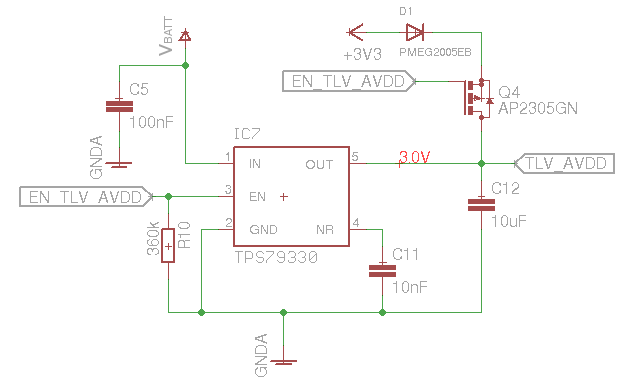

However, the TPS79330, being a low-noise/high PSRR design, consumes 170µA when on, hence I need to use its EN pin to turn it off when the device sleeps. To this end, I've designed the following circuit around it:

The idea being that,

- when the device sleeps, EN_TLV_AVDD is 0V, the TPS79330 is turned off (<1µA), and TLV_AVDD is supplied through the 3.3V rail, D1, and Q4. Thus the TLV320 will still receive AVDD, but it would be noisier

- when the device is active and needs to record audio, EN_TLV_AVDD is 3.3V, the TPS79330 is on (~170µA), and Q4 is off, preventing 3.3V/D1 from interfering

VBatt ranges from 3.3 to 4.2V.

This circuit assumes that the TPS79330 wouldn't mind if the output is at non-zero voltage with EN=0.

I have four prototypes assembled with this schematic, and all exhibit this strange behaviour:

- If I supply the VBatt rail from a bench PSU (which I assume ramps up the voltage smoothly) all is well - the LDO works as expected, and the powersaving scheme works too (e.g. with Vbatt=3.6V, and EN=3.3V, I get TLV_AVDD=2.99V; with EN=0V, TLV_AVDD is 3.06V and is noisier)

- If I use the actual battery (connection point is though a pin header), the LDO heats up a lot and does not work:

- device temperature is upwards of 120°C (measured with a thermal camera). If VBatt is high enough it exceeds beyond 180°C and one of the prototypes had the TPS79330 release its magic smoke

- the NR pin drifts around around 200mV

- the EN pin consumes a ton of current, as it is 0V if commanded 0V, but gets only to ~2.3V when commanded with 3.3V, I believe because of the MCU pin's limited drive capability

- Vout is basically Vin when EN=3.3V, and around 0 otherwise

I suspect a latchup, caused by the combination EN = 0V and noisy/uncoordinated rise on Vin and Vout (since the 3.3V rail comes from another LDO, fed by VBatt).

There's some slight variability as one of the device exhibits the problem on battery regularly, but not always. The other two have this problem every time. All devices work fine with the PSU supply.

Any idea of what's causing the latchup (if it is a latchup)? And how to resolve it?

I can poke around anyone has an idea what to try/measure.