Hi Team,

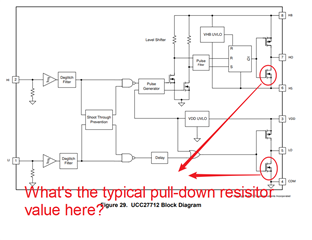

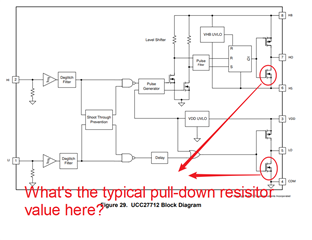

Customer wants to know what's the typical value of pull-down resistor of our UCC27712 here? And does UCC27712 integrate current-limit functions inside?

Best,

Stanley

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Customer wants to know what's the typical value of pull-down resistor of our UCC27712 here? And does UCC27712 integrate current-limit functions inside?

Best,

Stanley

Hello Stanley,

For the typical pull down resistance, is the datasheet parameters RLOL and RHOL which is 1.5 Ohms typical and 4 Ohms maximum. For the question of does the UCC27712 integrate current limit functions inside. It is not totally clear what you mean by current limit functions. There is not a function pin for external current sense (for the power train) and limiting or shutdown circuits.

For the driver output current, the peak drive current is determined by VDD and the sum of the driver internal resistance(s) and the external gate resistance including the FET internal Rg. If the resulting VDD combination and resistance results in high current result, beyond the driver ratings, the external power stage current is also determined by the internal driver devices internal drive voltage and device parameters (gain). The gate driver will self limit current due to this conditions, the user does not have to worry about limiting the driver peak current with external resistance to protect the driver.

Hi Richard,

Thanks for your helps. I don't quite understand below sentence you quoted above "If the resulting VDD combination and resistance results in high current result, beyond the driver ratings, the external power stage current is also determined by the internal driver devices internal drive voltage and device parameters (gain)"

Could you pls further clarify this here? Thanks.

Best,

Stanley

Hello Stanley,

What I was looking to communicate, is that the driver will "self limit" the gate drive current within the internal device drive current capability which is determined by the driver device parameters. The user does not need to worry about having a minimum external gate resistance for the purpose of limiting the gate driver peak current.

Regards,