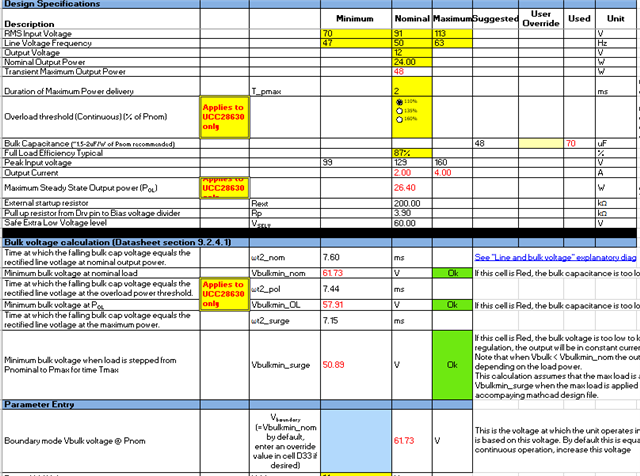

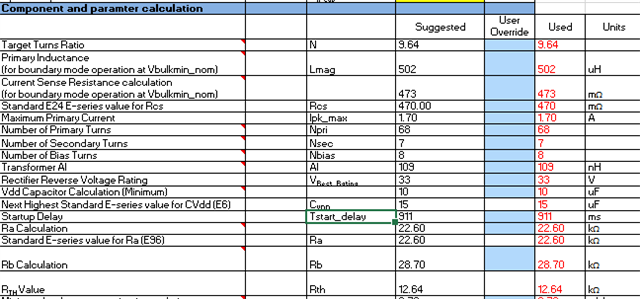

I'm troubleshooting a power supply design based off the UCC28634, and I've tracked it down to a fault code on the SD pin giving 25 - AC (i.e. bulk cap level) under-voltage detection before startup or restart

Codes taken from this thread - e2e.ti.com/.../ucc2863x-fault-cause-codes

I'm running it off a DC power supply set to 130v

I'm now looking for the next step to sort out this fault code.

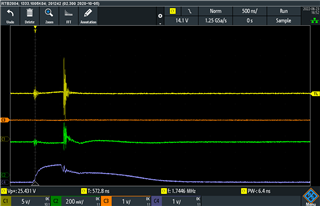

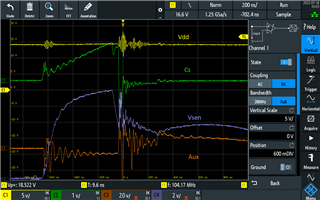

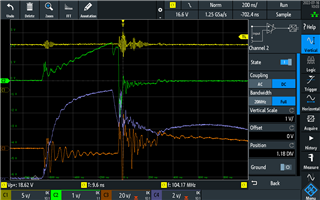

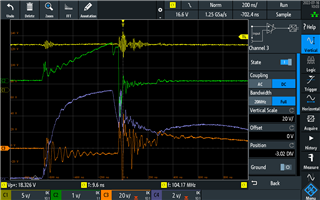

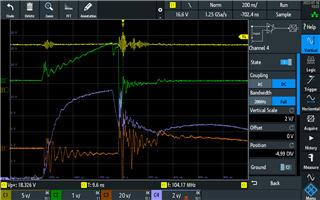

Green - SD pin

Yellow - Vdd pin

Orange - AUX Winding