Hello,

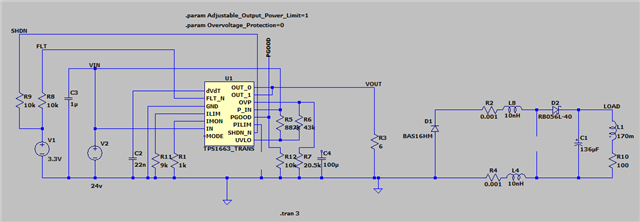

I have tried to simulate the basic operating features of TPS1663 in LTSpice, I have observed some unintended behavior during the simulation.

Below are the test scenarios…

Test case1:

Current limited to 2A

Load current is 1A(resistive load).

Observations: The output is loaded less than the Over current limit set (2A), So the output voltage is same as input and there in no FAULT which is expected behaviour. But the PGOOD signal remains LOW whereas it should be active HIGH for normal operation.

Test case2:

Current limit set to 2A.

Load current is 4A(resistive load)

Observations: The output is loaded more than the over current limit set (2A), the output current goes zero from trip limit (2A) at 0.2Sec, But it recover to trip limit at 0.9 Sec and it continuous. The output voltage goes up to 12V and become zero when the trip happens and recover to 12V again. The MODE pin is set for LATCH operation, but it is observed that the output is recovered. Also FAULT is always asserted irrespective of TRIP or not.

Could you please look into this observations mainly the unintended behavior of PGOOD and FAULT pins.

Attached the spice model used for simulation.

Regards

Hari K