Hi TI members,

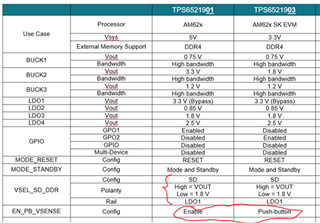

i have 2 questions about TPS6521901. from below diagram, we can see for EN_PB_VSENSE ,TPS6521901 is enable, but others support push-button, does it means TPS6521901 can not support HW pull GND to disable this PMIC? if we have push button application, how could we resolve this problem?

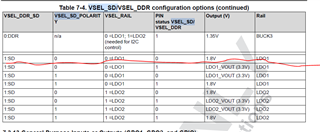

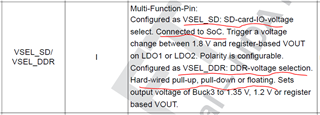

another question, for VSEL_SD_DDR the default config is SD mode, if we want the LDO1 output connect to SOC DVDD1.8V(fixed 1.8V), does that mean, the VSEL_SD_DDR connect to SOC(GPIO), and keep the GPIO low status. so the LDO could output fixed 1.8V?