Hi team,

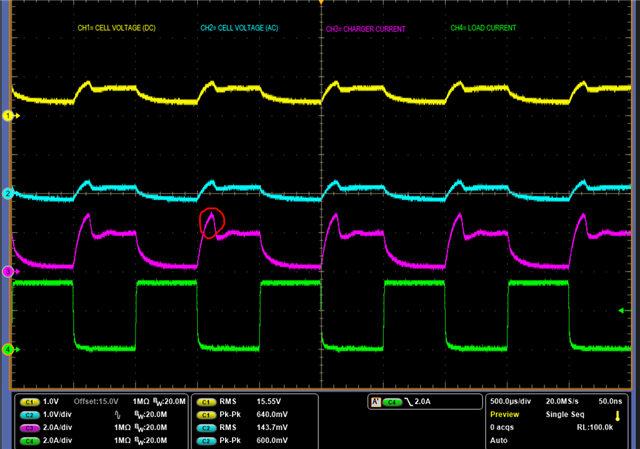

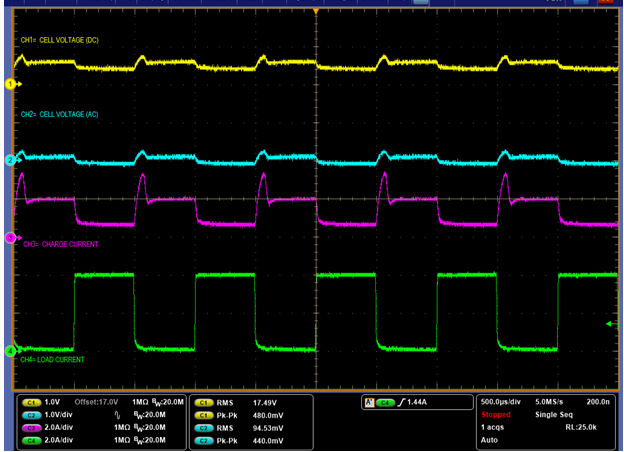

when customer performed the system load transient, you can see channel 3 the charge current has a prominent peak,

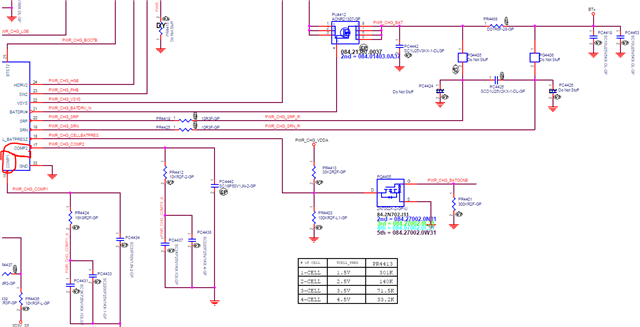

I know during input current limit, the BATDRV keep same voltage all the time , so I suspect this peak current may be caused by Vsys peak as you can see from channel 1 or 2.

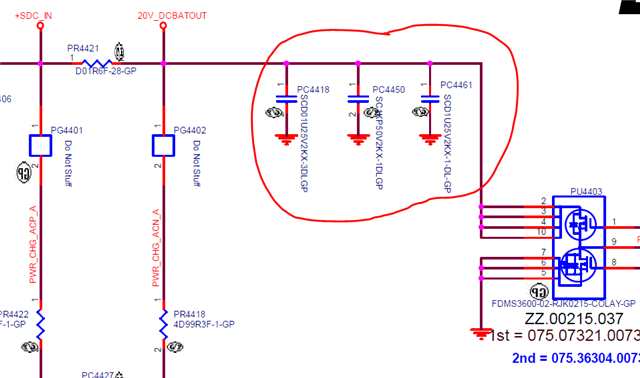

would you let me know how to minimize this peak current ?

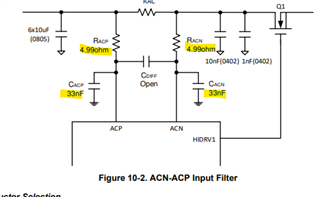

should we start from COMP component?