- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi support,

For TPS74701 implemented in one project, we have below configuration:

Input Voltage & BIAS voltage: 3.3 V connected together;

Output Voltage: 1.1 V

Current: 0.4 A

The 1uF input capacitor is near BIAS pin, there is no input capacitor near VIN pins.

What is the impact of using 1uF? stability issue, noise issue, reliability issue?

The datasheet recommends minimum 4.7uF input capacitance when Vin and BIAS are connected together.

Thanks,

Wei

Hey Wei,

The input needs a minimum 1uF capacitor and the bias rail needs a nominal value of 1uF.

Only using a 1uF capacitor for both rails could cause unpredictable behavior not characterized in the datasheet, especially because the capacitor is not near the input of the LDO.

This may cause stability issues.

Best,

Juliette

Hi Juliette,

Thanks for your quick reply.

The stability issue means the Vout will remain 1.1V but with higher noise amplitude, or means the Vout will be oscillating and eventually give up and shutdown?

I am trying to evaluate if this can be a long term issue for each board and impact for mass production with the 1uF capacitor value.

Can you elaborate more?

Thanks,

Wei

Hey Wei,

The impedance on both the rails needs to be kept low to keep the rails stable - meaning that in increased capacitor can help buffer noise and transients from the respective rails.

With the low capacitance, especially because it is not placed close to your LDO, a transient can cause the part to go into dropout.

Many errors can rise from this configuration and we do not recommend it [can be increased noise on either line, can be an output stability issue if the part goes into dropout and the input cannot recover]

However, if you do testing for your specific application and decide that the risk is minor, you can make the decision to keep the configuration.

Best,

Juliette

Hi Juliette,

After reading further of the LDO TPS74701 datasheet about the dropout mode and disable mode, I think we may have a marginal issue.

The same project, we also use TPS74701 for below power rail:

Input Voltage & BIAS voltage: 3.3 V connected together.

Output Voltage: 1.8V

Current: 0.02 A

The 1uF (not 4.7uF) input capacitor is 0.5'' away from both VIN and BIAS pin connected through 10mil width trace.

Do you have concern of this configuration?

Thanks,

Wei

Hi Juliette,

One last question, if Vbias drop below Vbias(min) = 1.8V + 1.31V = 3.11V in very short of time during transient, then LDO go to disabled mode and PG is pulled low.

And if Vbias is settle back quickly to be > 1.8V+ 1.39V =3.19V to after that event, does the LDO recover automatically to be normal function mode and PG signal is pulled high again?

Thanks,

Wei

Hi Wei,

I was out of office yesterday, I apologize for the delay in response.

For your first question, I do not recommend the configuration. Especially because the capacitor is far away from the input, various issues can come up. You should increase the input capacitor.

Please refer to section 8 of the Datasheet.

The PG pin will reflect the output of the LDO. If the device output recovers, the PG output will also recover. Because of the configuration with the small input capacitor, the transient will be reflected on the input and cause the output to take a long time to recover.

Best,

Juliette

Hi Juliette,

Sorry to bother you again. For Vbias(min) parameter, which make LDO go to disabled mode show in Table 1 in page 13 of datasheet.

Input Voltage & BIAS voltage: 3.3 V connected together.

Output Voltage: 1.8V

Load current: 0.02 A

What is the Vdo voltage to calculate Vbias(min) = Vout + Vdo (Vbias) shown in section 6.3? I need to know what is the Vbias threshold if the LDO go to disable mode.

Appreciate your quick reply.

Thanks,

Wei

Hello Wei,

I will check to see if we have any validation data that may be more specific to your case, but we typically approximate that from plots in the datasheet.

Best,

Juliette

Hello Wei,

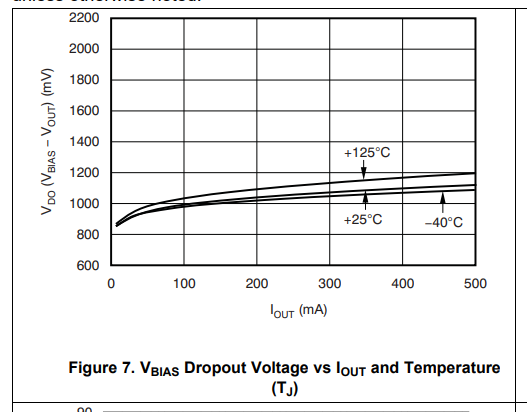

In the EC Table of the datasheet we include that the maximum dropout voltage for VBIAS is:

So with a lower current output:

It seems that the dropout voltage for VBIAS can be approximated to 850-900mV.

This means that the minimum voltage depending on your output would be 1.8V+875mV = 2.675V for your bias rail.

According to the note on table 6.3, this value is lower than 2.7V, so your minimum VBIAS voltage would be 2.7V for your application.

However, because I am approximating, it may be best to test this on your application just to verify that 2.7V will be enough.

Best,

Juliette