Other Parts Discussed in Thread: UCC14240-Q1, UCC25800

Hi,

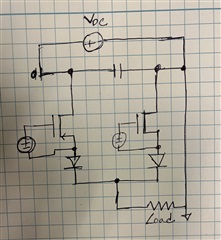

I am planning to use two SiC MOSFETs in two branches with different drain and source potentials (schematic is pasted here for reference). As the sources are at different potential due to configuration, it will impact the power supply configuration of the gate driver ISO5852S. The grounds (GND2) of the power side supplies (VCC2 and VEE2) of ISO5852S are the same, thereby essentially shorting the sources of the MOSFETs in different branches if I use same DC power supply for both MOSFETs. As this is an isolated gate driver IC, I am under the impression that the shorting of the grounds of (VCC1) at the control side will not impact the operation of the circuit.

Please suggest how to configure the power supplies for the gate driver ICs to drive the MOSFETs in two branches in the said configuration shown in the picture below without shorting the sources. Thanks in advance.