Other Parts Discussed in Thread: TPS65916, AM5716, TPS65919-Q1

Dear Experts,

we are designing a new board with AM5716 and the PMIC TPS65917-q1, previously we had the TPS65916 but this is not available any more.

My reference are: SLVSCO4D (TPS65917-Q1 datasheet) and SLVUAX9E (TPS65919-Q1 and TPS65917-Q1 User's Guide).

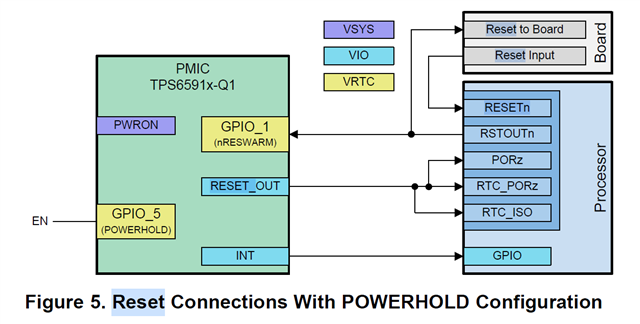

I have the architecture like in Figure.5 where a FPGA drives the EN (POWERHOLD-GPIO_5 pin of TPS65917) and the Warm Reset (RESETn pin E23 of Sitara). BOOT=1 (connected to LDOVRTC_OUT)

From SLVUAX9E par. 6.3: "A warm reset is triggered by setting NRESWARM (GPIO_1) low, which causes the OFF2ACT sequence to be executed regardless of the actual state (ACTIVE, SLEEP), and the device returns to or remains in the ACTIVE state. [...] Additionally, if BOOT=1, then RESET_OUT is asserted low during the worm reset sequence. [...] If BOOT=1 is used, then the PMIC must be enabled by the POWERHOLD (GPIO_5) pin.[...]. If POWERHOLD is set to GND while BOOT=1, the PMIC will shut off during the warm reset sequence."

My issue are:

- RESET_OUT doesn't go low when I drive low RESETn of SItara that drives low NRESWARM (GPIO_1) of the PMIC. ARM15 stops working and I have to power off and on.

- NRESWARM (GPIO_1) and POWERHOLD (GPIO_5) both LOW ARM15 stops working and I have to power off and on.

With PMIC TPS65916 I have to drive LOW and then HIGH both NRESWARM and POWERHOLD in order to have RESET_OUT low and a reboot of the system.

My three goals are:

- turn on the system -> OK this works

- reboot Sitara changing boot sequence -> KO and Sitara freezes (with TPS65916 was OK)

- turn off the system -> KO

Can you help me?

Best regards

Francesco