Other Parts Discussed in Thread: UCC2895, , UCC28951, UCC3895, UCC1895

Hi Team,

I used to query in the following thread, but since it was already closed, I created a new thread. Please tell me about this issue again.

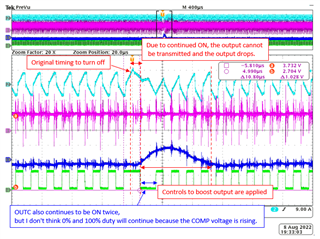

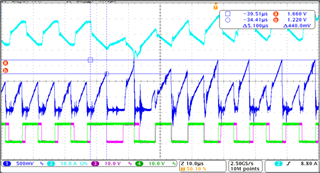

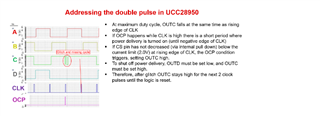

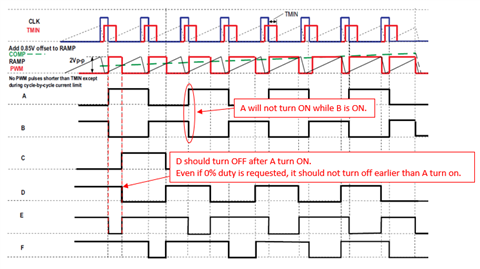

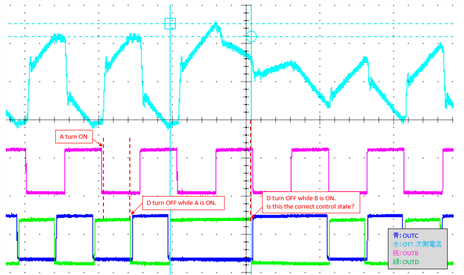

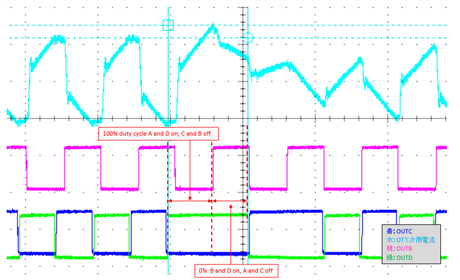

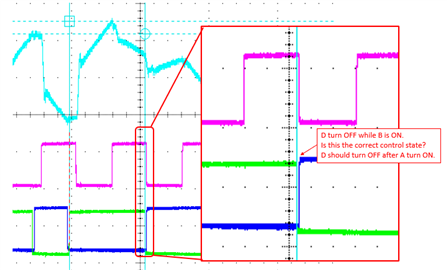

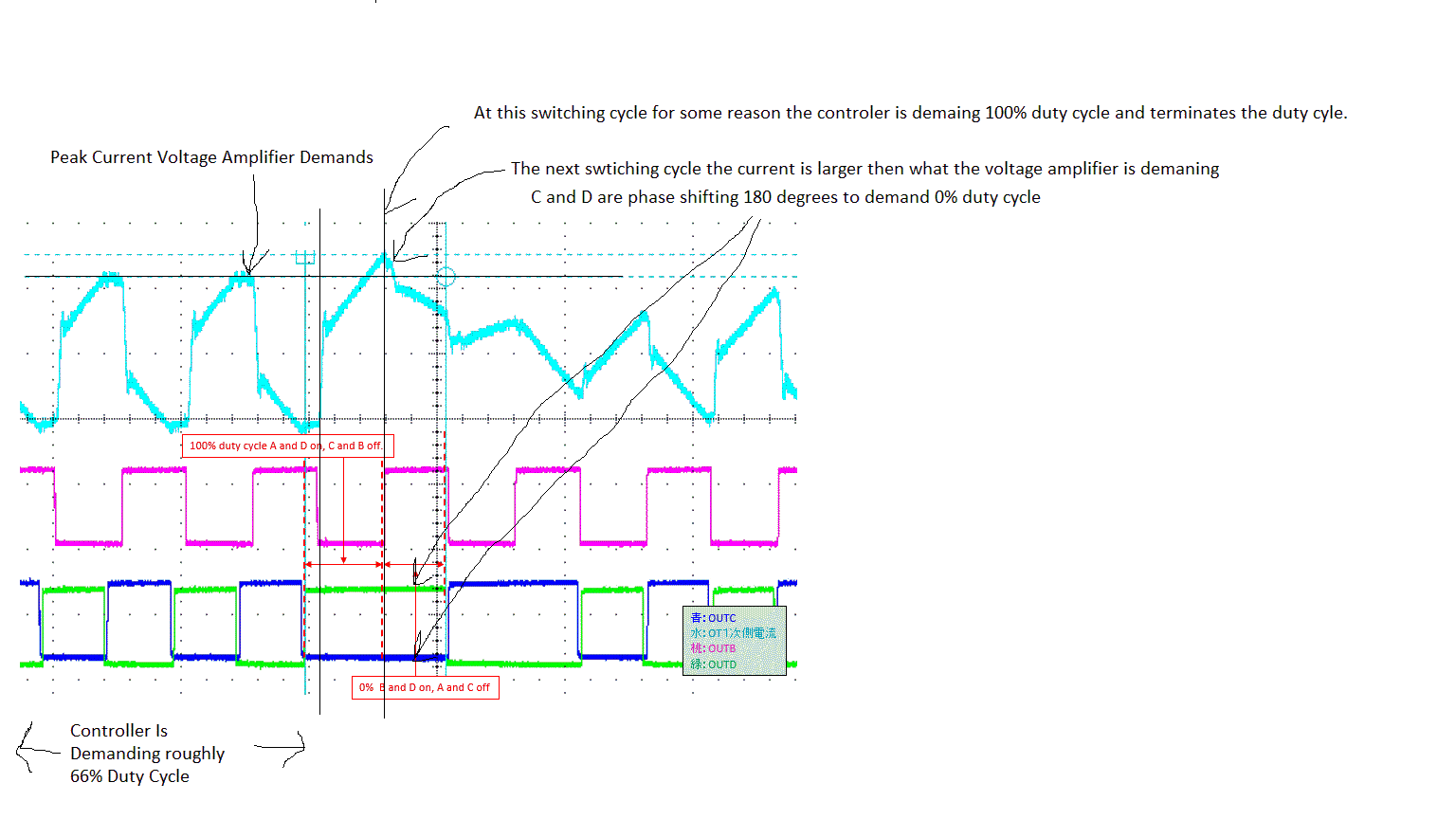

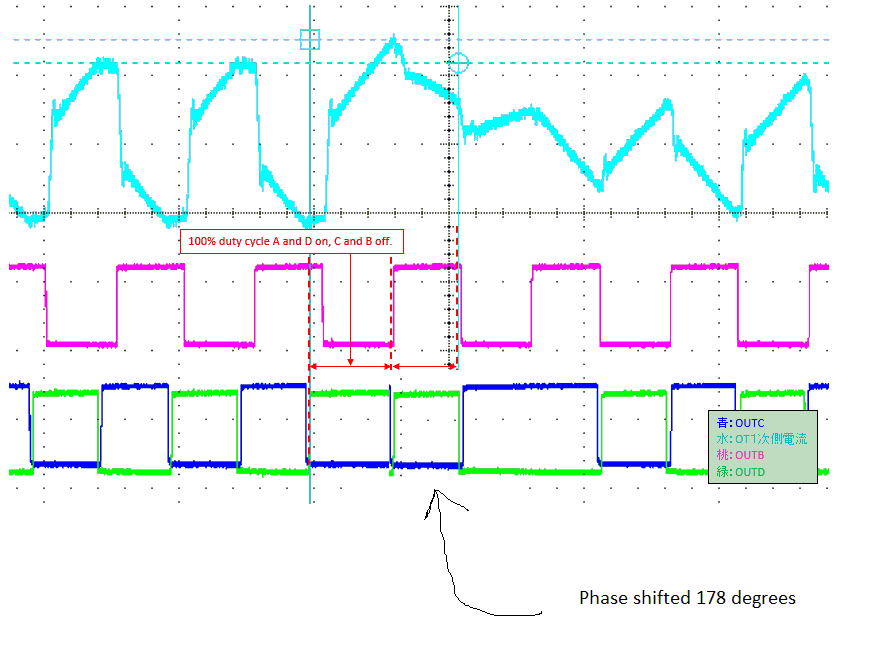

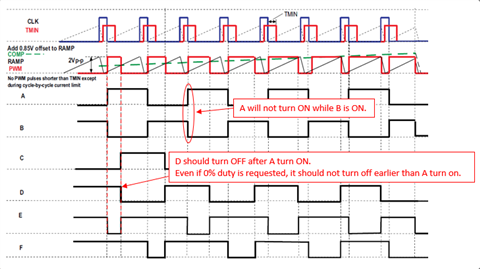

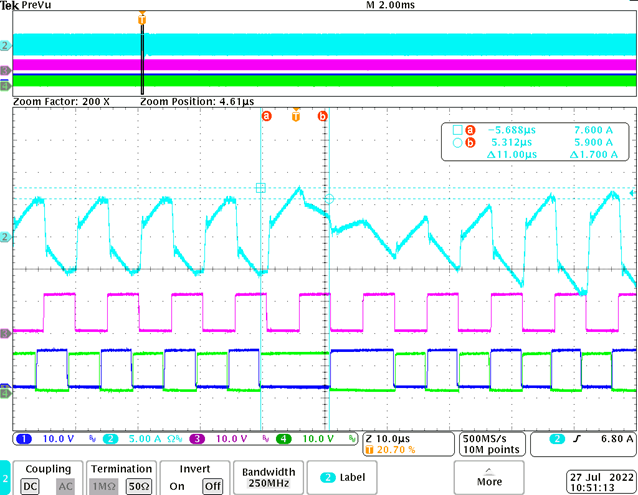

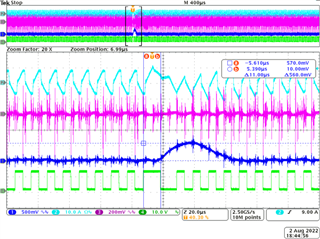

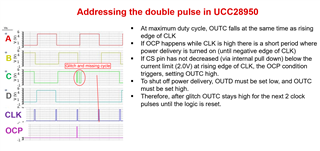

There is a problem that the pulse width of OUTC and OUTD becomes long irregularly.

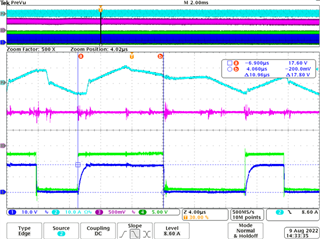

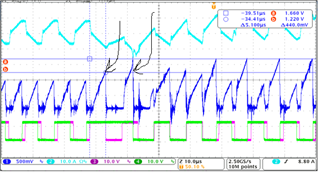

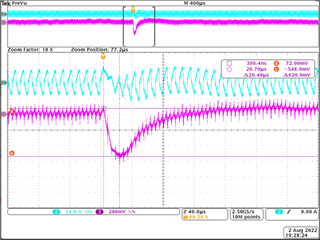

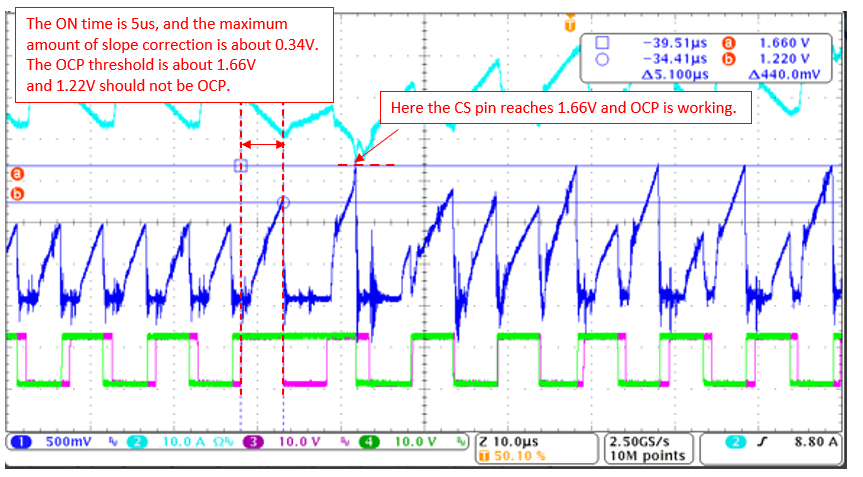

As instructed, I checked the waveforms of the CS pin and COMP pin, but it seems that there is no abnormal waveform at the timing when the problem occurs.

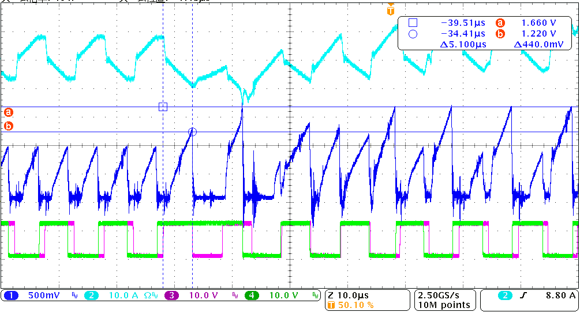

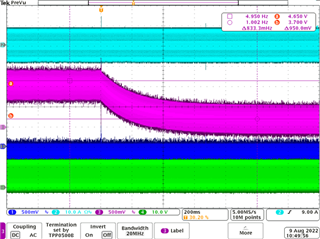

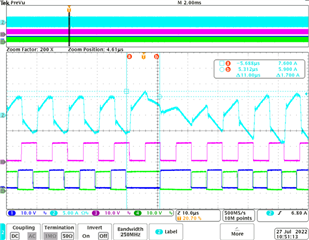

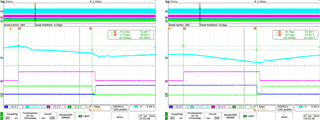

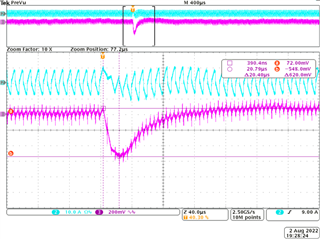

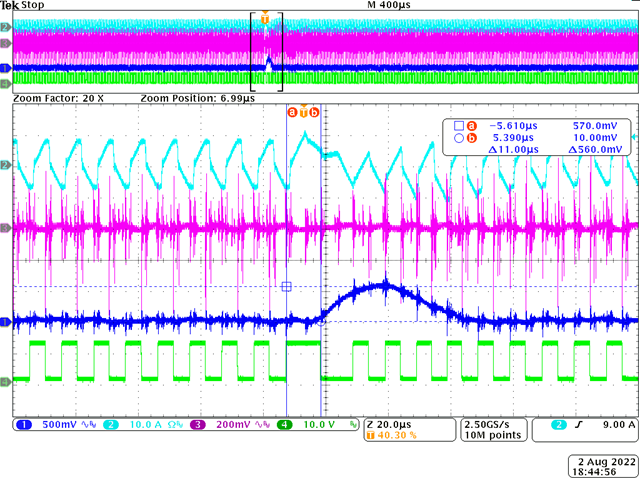

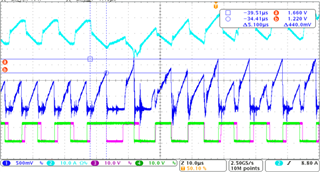

CH1:OUTC, CH2:Transformer Current, CH3:OUTB, CH4:OUTD

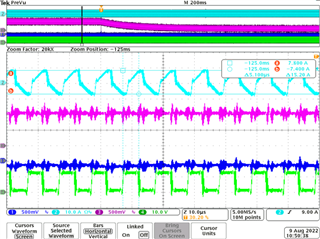

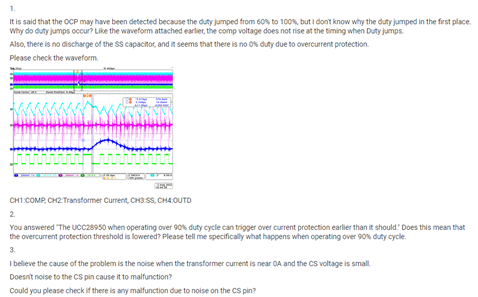

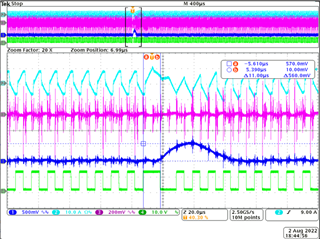

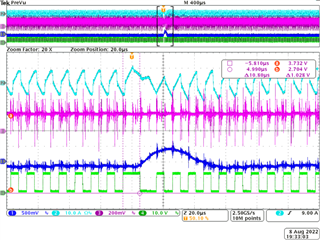

CH1:COMP, CH2:Transformer Current, CH3:OUTB, CH4:OUTD

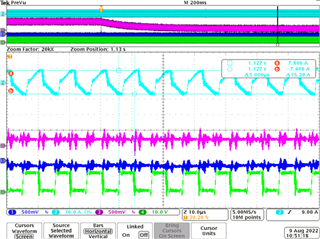

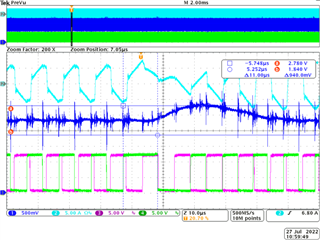

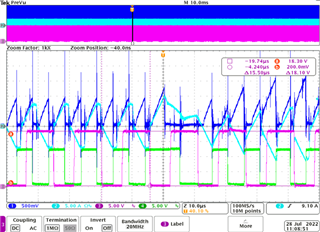

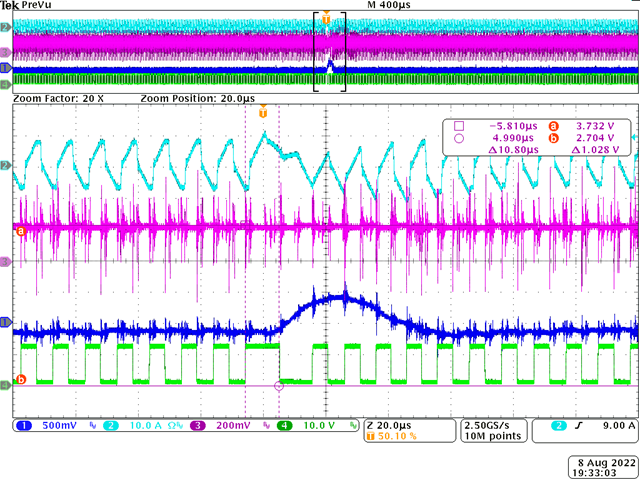

CH1:CS, CH2:Transformer Current, CH3:OUTB, CH4:OUTC

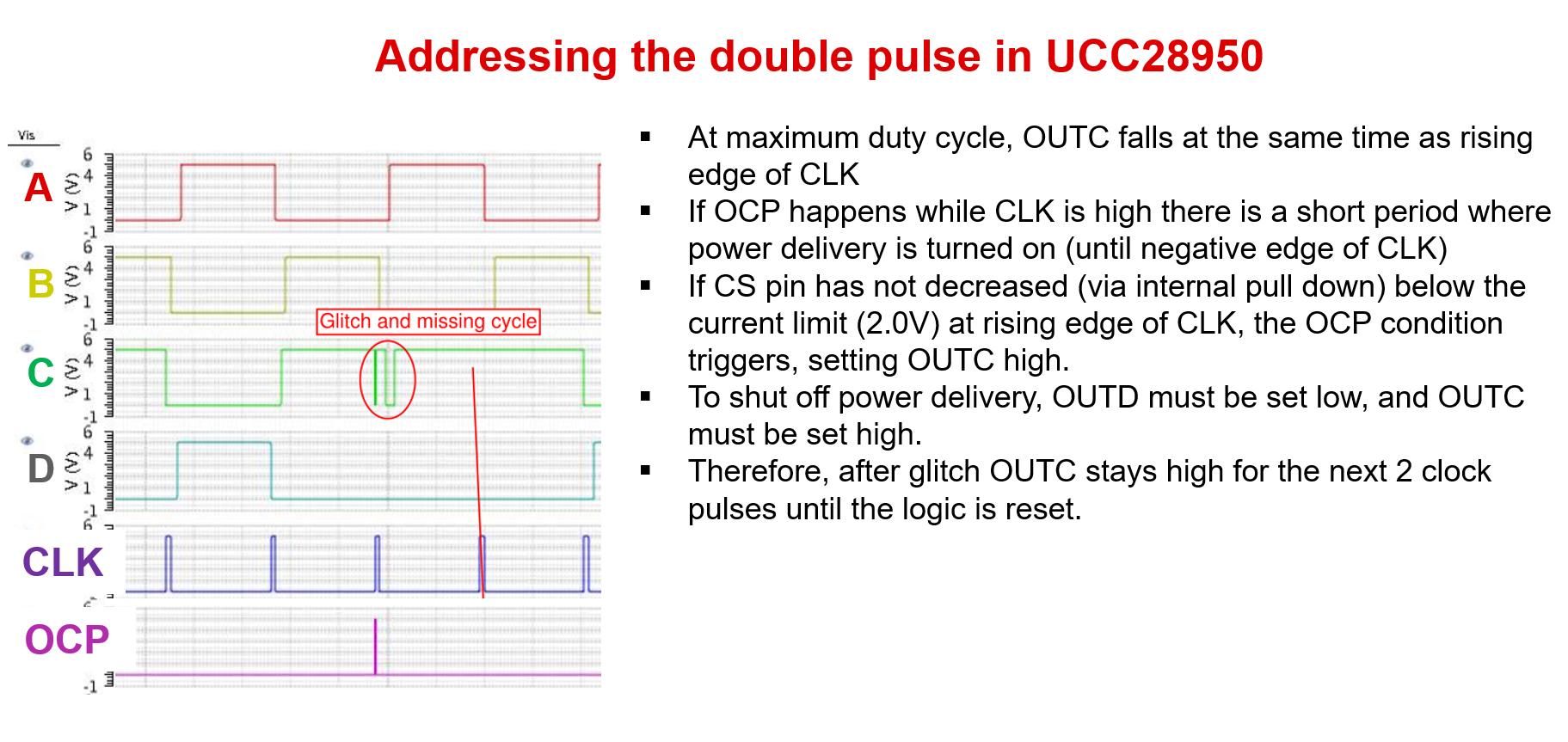

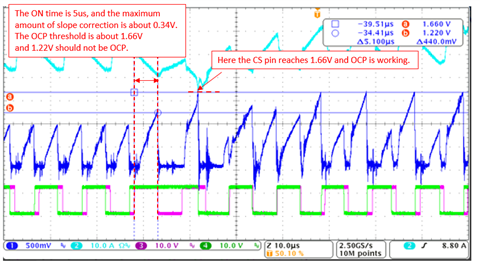

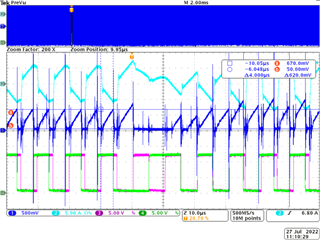

As additional information, when the pulse width of OUTC and OUTD becomes long, it seems that it is turned off at a value close to the maximum Duty.

CH1:OUTC, CH2:Transformer Current, CH3:OUTB, CH4:OUTD

Please explain the mechanism of the above operation.

Best regards.

.

.