TI experts,

I notice if LD pin is higher than 1.4V, then BQ76952 shutdown sequence will pause until LD pin drop lower than 1.4V. I wonder after LD pin drop lower than 1.4V, how long need to shutdown BQ76952 or turn off REG18?

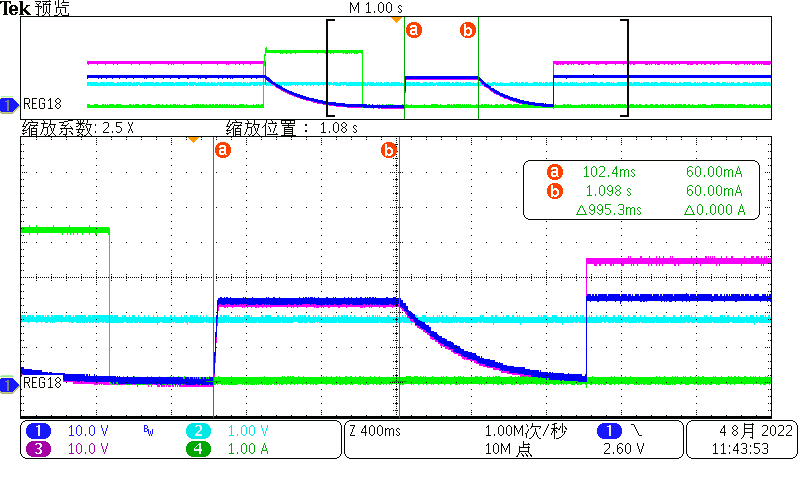

In my 1st test as shown in FIG.1, the DSG/CHG FET were on, then start shutdown command. With DSG FET turn off, the LD pin voltage is droping from VBAT. After LD pin drop below 1.4V, it takes 52ms to shutdown REG18.

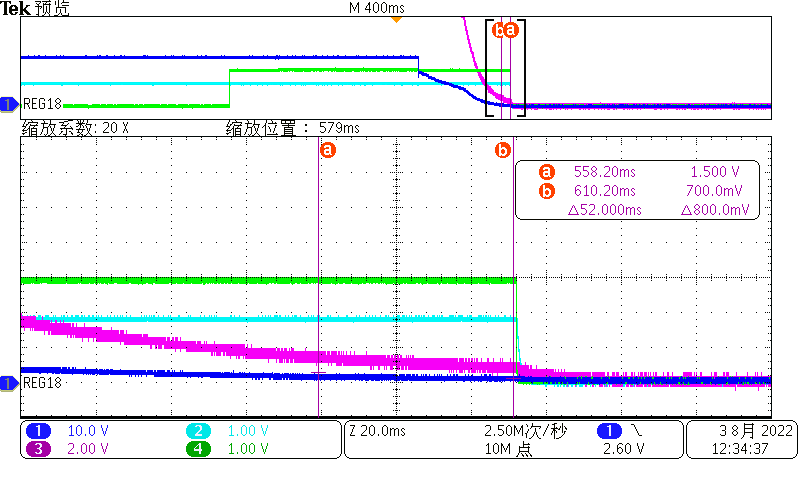

However in my 2nd test as shown in FIG2, the DSG/CHG FET were off, but 3.3V voltage was on LD pin. Then, start shutdown sequence and turn off 3.3V on LD pin. It can be seen after LD pin drop below 1.4V, it takes 241ms to shutdown REG18.

So, what's the exactly shutdown sequence? It relates how long need turn off DSG/CHG FET after shutdown my BMS system.

FIG.1 CH1 DSG PIN, CH2 REG18, CH3 LD PIN, CH4 RST_SHUT PIN

FIG.2 CH2 REG18, CH3 LD PIN, CH4 RST_SHUT PIN