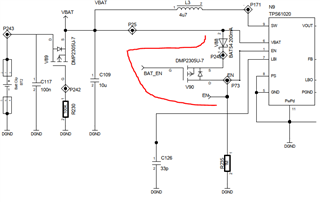

Hi,

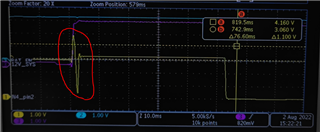

I am using TPS61020 with 3V battery VBAT voltage. Enable pin is handled thorough external MOSFET as shown below. At start up , when I enable MOSFET V90 ( BAT_EN = 1) , I see glitch on EN pin, which is going upto 7V. This is observed at Drain of MOSFET V90. But it is not seen at Anode of V88. What can be the reason for this ? whether this is acceptable ? How this can be avoided ?