Hi

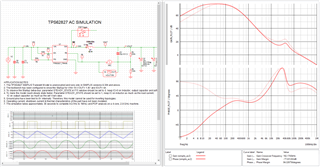

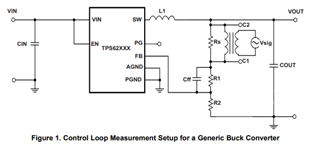

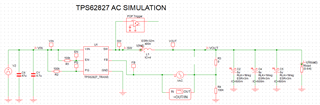

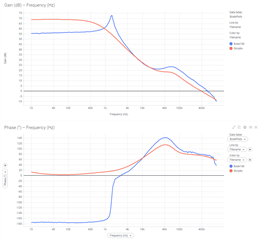

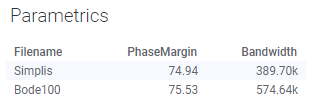

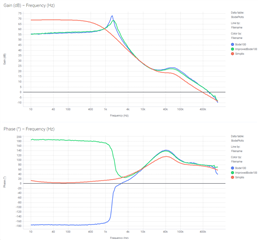

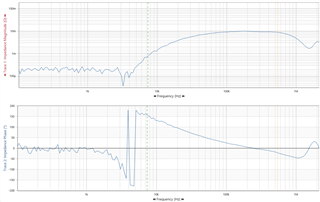

I cannot find the stability simulation tool as Bode Plot in the WEBENCH POWER DESIGN,

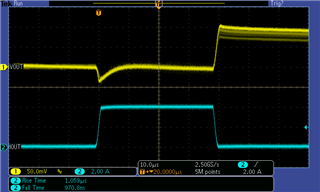

Could you please help to check whether this application is feasible?

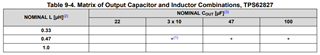

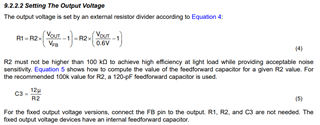

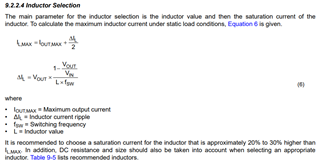

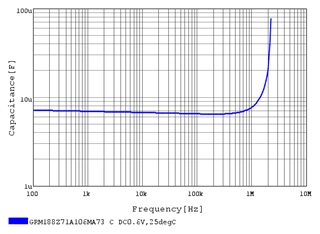

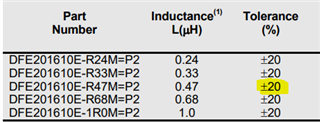

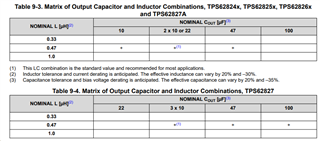

We are going to evaluate the suitable network of voltage divider other than the typical one as datasheet discoursed.

Regards

Ben