Other Parts Discussed in Thread: TPS544C25, TPS544B25, TPS546C20A

Hello,

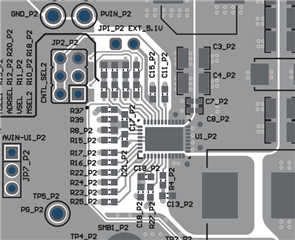

In the Layout Example section of the TPS546D24A datasheet, there is an un-named purple plane. Could you please advise what this plane is?

Thank you,

Kyle

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

In the Layout Example section of the TPS546D24A datasheet, there is an un-named purple plane. Could you please advise what this plane is?

Thank you,

Kyle

Hi Kyle,

Thanks for your question.

See the user Guide for a better Layout representation. That area is to represent where the component will be placed and can be left un-poured.

Thanks!

Tahar

Hello Tahar,

That is a pretty obscure shape (purple on the datasheet) that seems to affect the shape of the AGND (blue). Could you just confirm for me that it's not a pour in the datasheet layout.

Thank you,

Kyle

It is not intended to be a pour or represent a specific shape or net.

As Tahar mentions, it represents fan-out, routing and component area that the analog ground must be routed around.

Hello Peter,

Thank you. I think where we get confused is in similar layout recommendations in other datasheets, which have nearly an identical shape but a different purpose. This purple shape in other documents refers to an internal plane that is intended to reduce bypass parasitics. Below are some examples.

TPS544C25, TPS544B25 - pg 88 Item L

TPS546C20A - pg 88 see note re BP3 bypass parasitics

TPS546D24A - pg 167 see note re VDD5/BP1V5 bypass parasitics

Just to put me at ease and hopefully bring an end to my confusion, does this not serve the same purpose as those in the examples above?

Thank you,

Kyle

Yes, the note in Figure 10-1 on page 167 of the TPS546D24A datasheet has the same meaning as the note in Figure 10-1 on page 167 of the TPS546D24A datasheet.

It is best to connect the BP1V5 and AVIN bypass capacitors back to AGND through an internal layer back to a via as close to the AGND pin as possible in order to minimize mutual current flow from these bypass capacitors through sensitive nets, such as the pin detection ground references and it is recommended that VDD5, AVIN, and BP1V5 bypassing connections use multiple vias when changing layers to minimize added inductance in those paths.

That was not the intent of the purple plane, but if it helps clarify things, you can consider the violet area as an internal AGND plane to bypass BP1V5 and AVIN to the AGND pin separately from the other AGND connections.