At no load, what should the OUT point of the LM5020-based flyback converter and the waveform between the drain and source of the MOSFET look like?

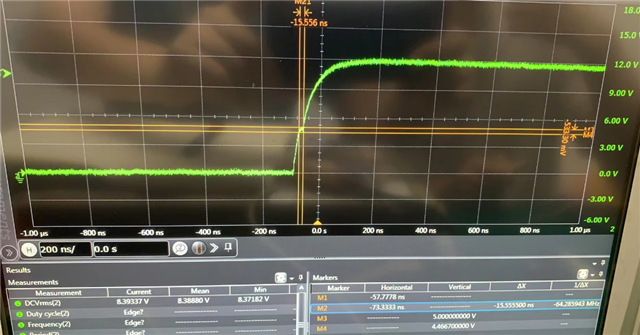

Is the waveform below normal? (voltage between drain and source of MOSFET)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

At no load, what should the OUT point of the LM5020-based flyback converter and the waveform between the drain and source of the MOSFET look like?

Is the waveform below normal? (voltage between drain and source of MOSFET)

Hello Charlie,

Thanks for reaching out to us via e2e.

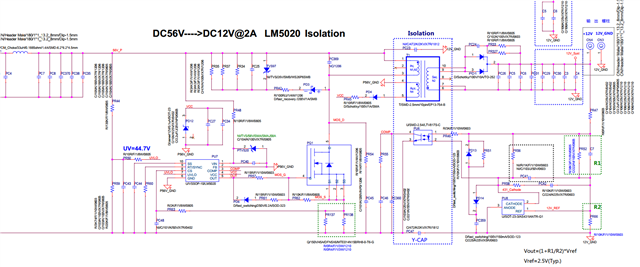

Can you please provide me with more details (input/output voltages and current), which type of feedback (primary/secondary/non-isolated)?

Ideally you could also share your schematic.

Thanks and regards,

Harry

Fig.1 is the waveform of point OUT, and Fig.2 is the schematic diagram of the circuit. Thanks.

Hello Charlie,

Thanks for the additional information.

You should see short pulses at the gate of the FET when the FET gets closed and the voltage at the switch node (Drain) reaches the minimum. The oscillations while the FET is off are normal.

Is there anything in particular that you are worried about?

Thanks and regards,

Harry

Hi Harry,

Thank you for your reply. When there is no load, in the waveform of the OUT point, the duty cycle is very small and the pulse is extremely narrow.

What I want to know is why does the voltage at point D (approximately equal to the voltage across DS of the MOSFET) oscillate?

What is the reason for the oscillation? Is it related to the parasitic capacitance of the MOSFET?

Best Regards

Charlie Xiao

Hello Charlie,

The oscillations while the FET is off are normal and expected.

They happen between the inductor (transformer) and various real and parasitic capacitances on the board.

Best regards,

Harry