Hi team,

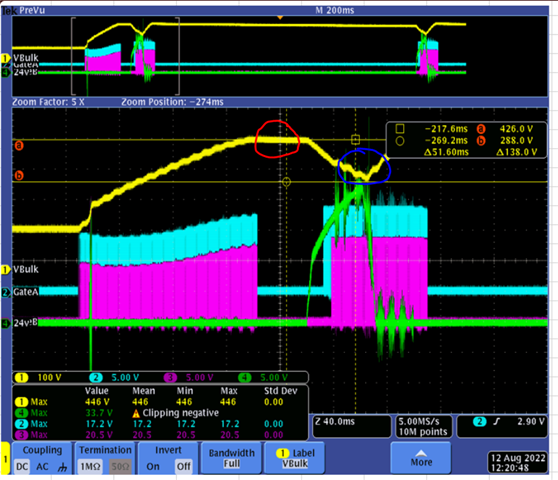

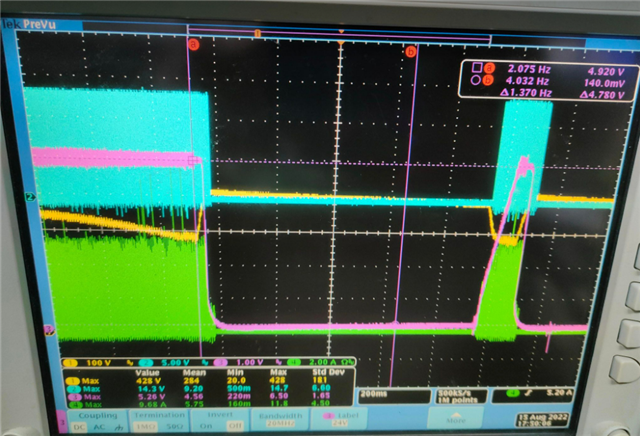

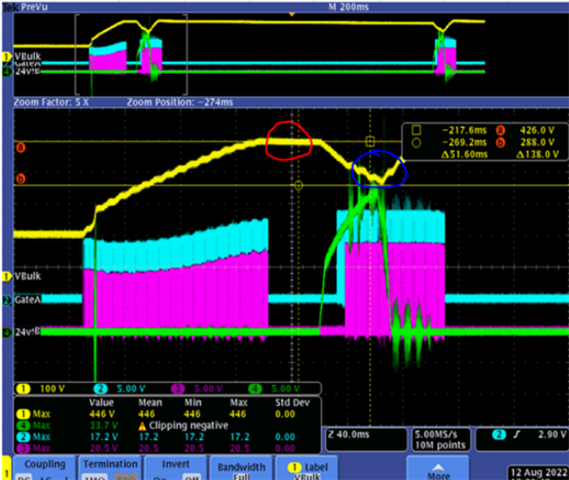

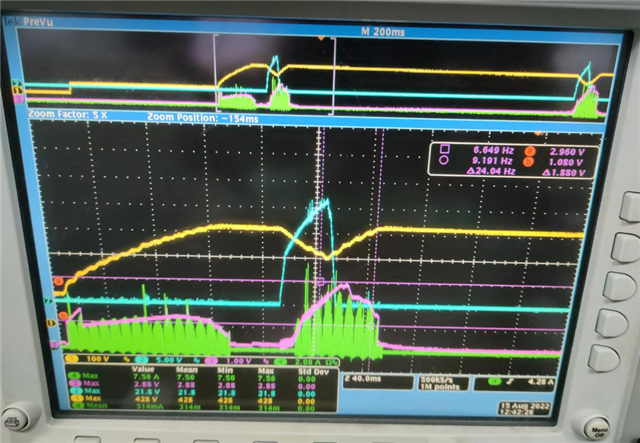

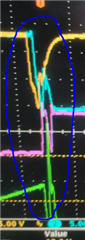

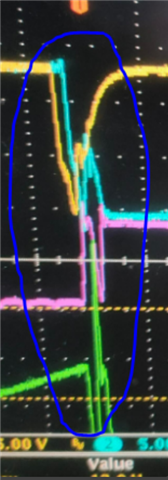

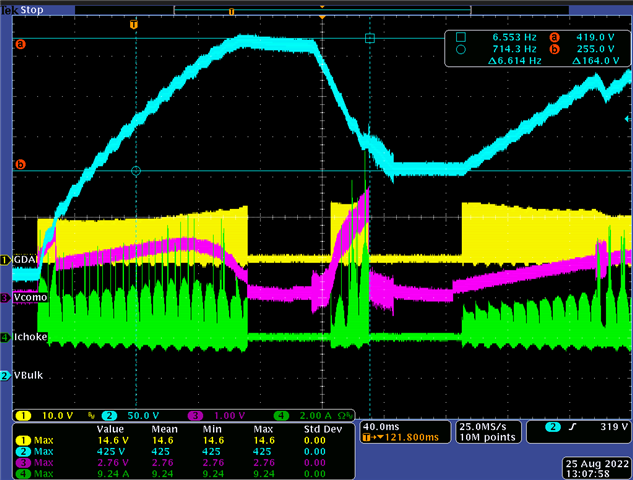

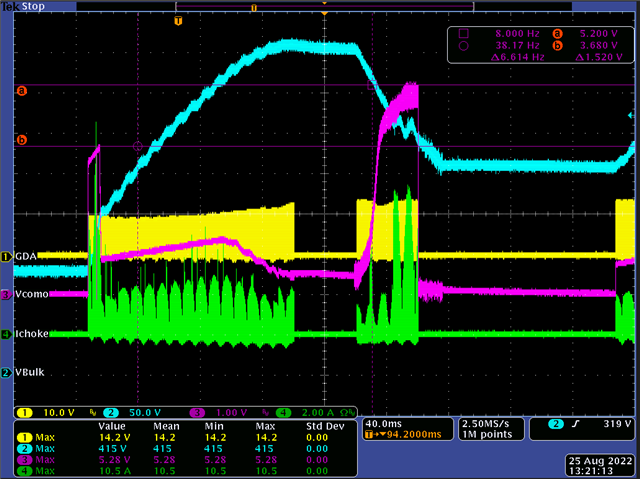

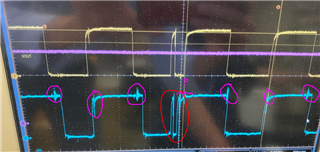

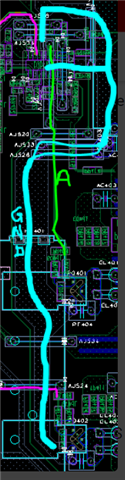

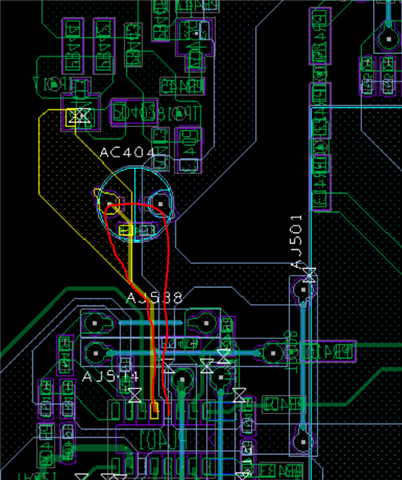

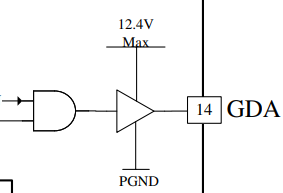

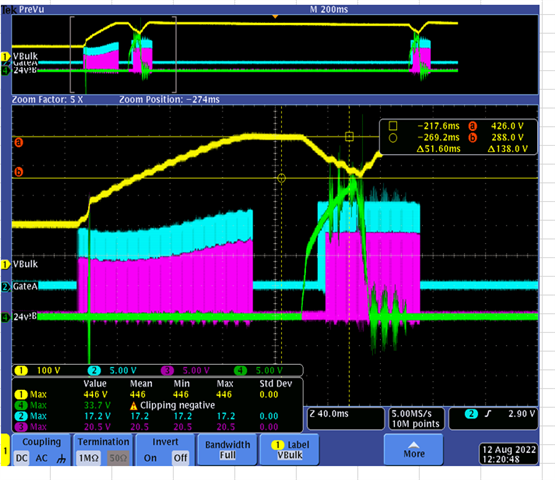

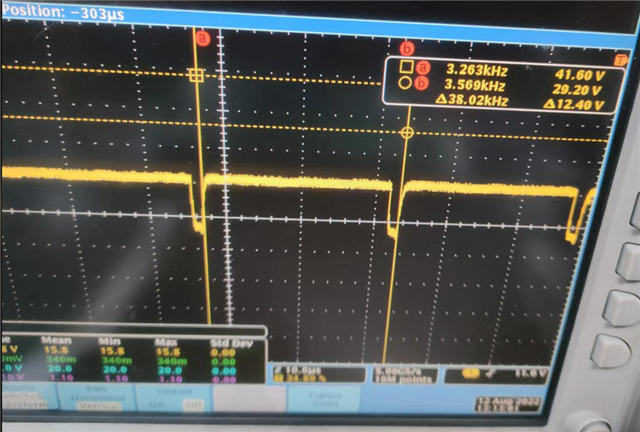

my customer found its PFC output drop to 288V when at higher power load which cause LLC shut down, we suspect this might be OVP since the output reach 426V which is above OVP 422V,

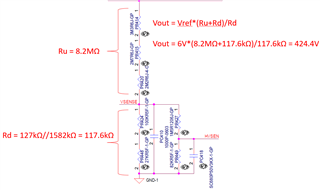

I wonder why this OVP happen if most of the parameters follow calculator tool,

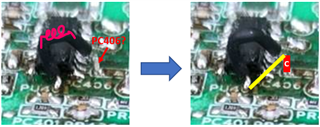

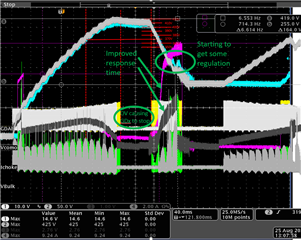

what action can we take to avoid this?

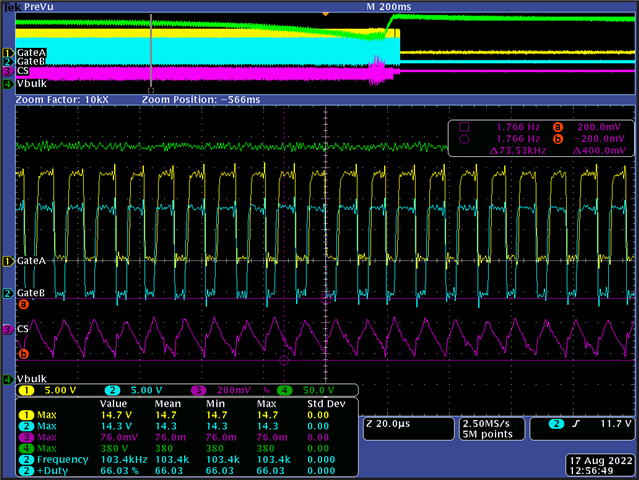

BTW, duty cycle is 95%

below excel is the issue organized by them , please refer to it for more detail.