Other Parts Discussed in Thread: TIDA-010208

Hi

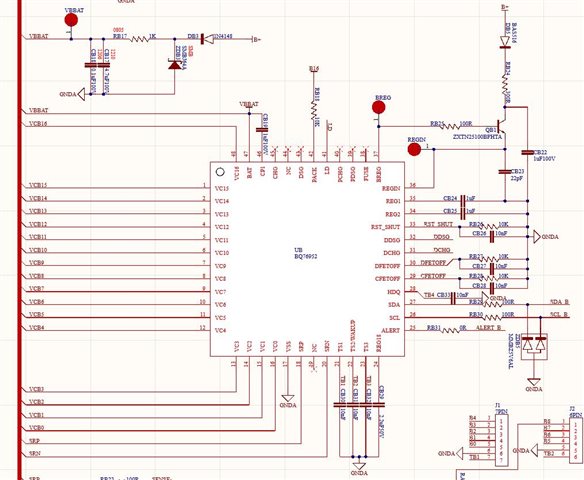

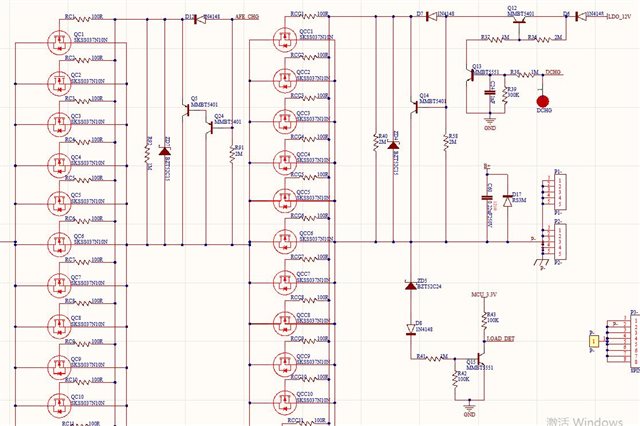

The customer test with the BQ76952 board which they designed. They use the non-contact ± 15kV to test the CAN communication port, and find 8. 9. 10 pin damage.

Total test with 8 pieces, and all of them have the same phenomenon.

How to improve this issue?

Thanks

Star