Hi all,

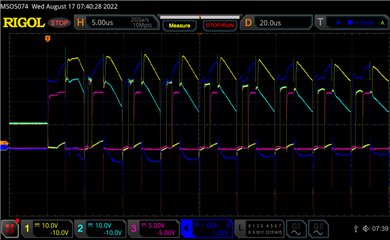

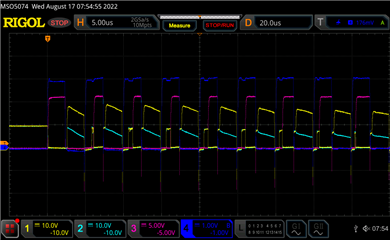

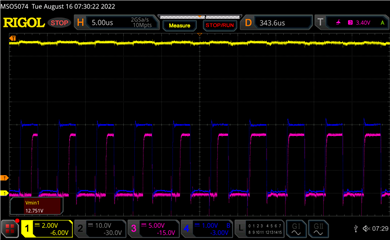

As the title suggests, the output of the low-side gate driver does not follow the input correctly as you can see in the picture below.

- CH1: Supply voltage

- CH3: Output of gate driver (LO pin)

- CH4: PWM input (LI pin)

The gate-driver does turn of at the correct moment but the turn-on is significantly delayed which leads to shorter pulses.

There are 4 drivers in the circuit, each showing the same problem.

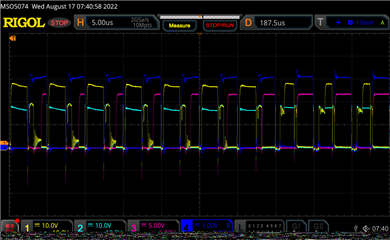

What is also strange is that the driver starts to operate normally after 100µs (see next picture).

Some additional information which might be help to find the problem:

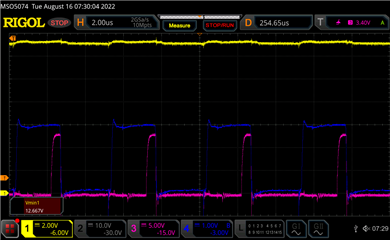

- The supply decoupling capacitance is 4.7µF (and I don't think this is the problem since the supply is not dropping below the UVLO)

- Gate resistor is 10R and the MOSFETs gate capacitance is around 3nF

- Switch node voltage is 30V

- LI and HI have 1nF of decoupling capacitance directly at the input pins of the driver

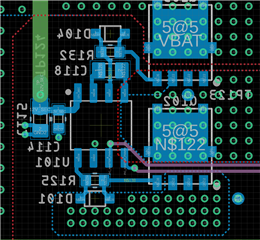

Below you can see the PCB layout:

Any help is highly appreciated.

Thanks in advance.