Hello Team,

One of my customer is using a 100V MOSFET from competition in below configuration and looking for alternate source.

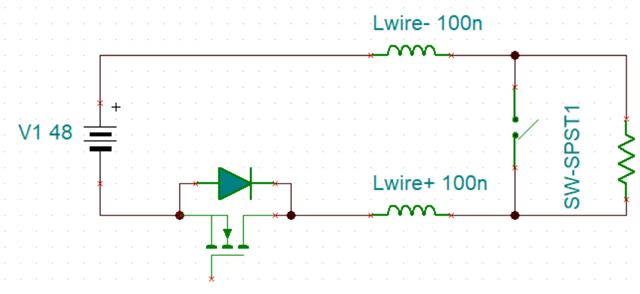

They have multiple MOSFETs in parallel in return path of battery as shown below, close to battery.

Load on extreme right is connected through long wires, hence wiring inductance is shown using Lwire- and Lwire+.

If there is short condition across load as shown using switch in below diagram, it creates a huge inductive current spike of 1500A for ~40uS.

During this transient time MOSFET turns off, but VDS waveform looks to be clamped at 120V during inductive kick (although MOSFET rating is only 100V). Even with repeated trials for such short circuit, they are not able to fail MOSFET during such condition, although its exceeding rated 100V. and it always gets clamped at 120V.

Customer would like to know, if this type of clamping is expected for all MOSFETs or does TI MOSFET will also show similar clamp behaviour?

If there is some additional clamp required internally or externally to protect MOSFETs in such cases in general?

Kindly help to clarify.

Thanks you.

-Mahendra