Other Parts Discussed in Thread: TPS27S100

Hi everyone,

Here are a few questions about TPS1H000:

As you can see in below picture screenshot from datasheet. There is an internal clamping between Drain and Source to

protect this IC from a reverse voltage by inductive loads.

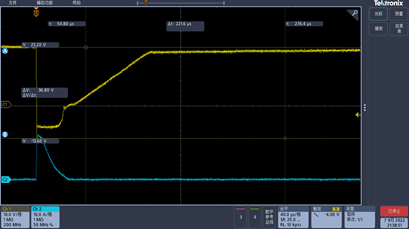

When we powered the VS 23V and used a TVS to clamp the -1.1kV surge voltage to -40V, but the IC was broken.

1. My question is how much reverse voltage and how long can this internal clamping withstand?

We also do test: power the OUT a -24V and power the VS 23V, which means the Vds is 48V,the IC work well.

2. Do you have any experience in this area or similar application scenarios? How many volts do you need to clamp the backpressure at?

3. According to the datasheet all the absolute maximum voltage are base on Device GND.

What is the maximum voltage between “CL” and “OUT”, “IN” and “OUT”?

Of course I welcome more notes and suggestions from you.

Thanks and waiting forward to your reply.

![]()